Синхронное образование Е2. Циклования структура. Назначение и принцип. Контроль качества передачи.

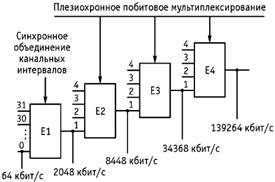

Принцип плезиохронного мультиплексирования состоит в следующем: o объединяемые цифровые данные, имеющие различные тактовые интервалы (в известных нормативных пределах), должны быть синхронизированы, т.е. согласованы по фазе и частоте тактов; o для синхронизации объединяемых данных должен быть применен буфер памяти; o Рисунок 2.4 Иерархическая схема мультиплексирования PDH

o в процессе записи данных в буфер и считывании могут образоваться в случайные моменты времени состояния неопределенности: o период записи T зап > периода считывания T cч, в этом случае буфер может дважды считаться, т.е. произойдет ложная двоичная единица; o период записи T зап < периода считывания T cч, в этом случае буфер может оказаться на момент считывания “пустым”, т.е. произойдет ложная двоичная единица. Для устранения указанных неопределенностей используется метод стаффинга, сущность которого поясняется с помощью рисунков 2.5, 2.6. Положительное согласование скорости в буферных устройствах предполагает заведомо более высокую скорость считывания двоичных данных из буферов, чем скорости записи, которые зависят от стабильности источников тактовых частот формирователей цифровых данных. Такты считывания для Е2 поступают со скоростью 2052 кбит/с, что гарантирует только положительное согласование. При этом через определенное время будет проявляться ситуация неопределенности, когда одни и те же данные будут считываться дважды (рисунок 2.6).

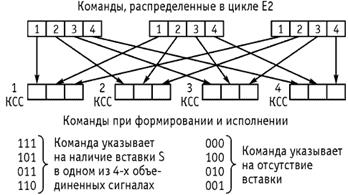

Рисунок 2.6 Проявление неопределенности и формирование вставки Ситуация неопределенности должна контролироваться временным детектором, измеряющим разность фаз записи и считывания . Образование неопределенности приведет к формированию вставки (бит S рисунок 2.6), которая выравнивает скорость и не допускает ложное считывание. При этом в структуру цикла Е2 помещается команда согласования скорости (КСС). Принцип формирования КСС и ее содержание изображены на рисунке 2.7. Т.о. в цикле Е2 передаются четыре независимые друг от друга команды согласования скоростей, представленные тремя битами. Истинность команды определяется по двум или трем одинаковым битам. Распределение команд по циклу и использование выбора 2 из 3 применены для повышения помехоустойчивости передачи КСС. В приемной части системы передачи с Е2 процедура демультиплексирования происходит с обнаружением и устранением вставок в каждом из четырех потоков данных Е1. Для этого восстанавливается тактовая частота каждого Е1, которая применяется для работы фазового детектора демультиплексированного Е1. Команды КСС и разность фаз служат вычислению вставки S и ее устранению.

Рисунок 2.7 Команды согласования скоростей

(Также смотри вопрос 23) Процедуры контроля ошибок передачи. Использование избыточного кода

CRC-4

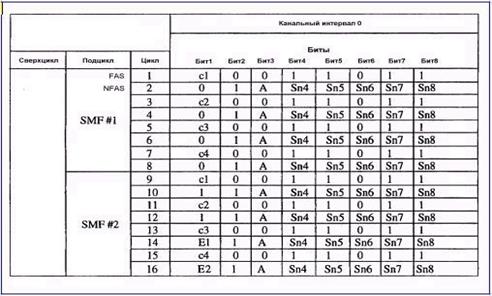

Рассмотрим механизм передачи информации о CRC- 4. Для передачи этой информации используется сверхцикловая структура. Однако, сверхцикл CRC-4 не обязательно связан со сверхциклом MFAS. Каждый сверхцикл может быть разбит на 2 подцикла (SMF). На рисунке ниже они отмечены как SMF#1 и SMF#2 и содержат по 8 циклов каждый. Соответственно отмечены по 4 бита, используемые для передачи CRC-4 каждого сверхцикла (биты С). Биты CRC-4 вычисляются методом деления двоичной суммы содержания 8 последовательных циклов на тестовый полином, остаток от деления в виде 4-битового сообщения вставляется в следующий сверхцикл для передачи в потоке Е1.

В четных циклах NFAS битами Si передается сообщение сверхцикловой синхронизации CRC-4 - комбинация 001011, которая используется на приемной стороне для синхронизации по CRC. Кроме этого в составе сверхцикла SMF, передается его главная информация - сообщение C1C2C3C4. В качестве дополнительного сообщения, передаваемого в направлении передачи при обнаружении ошибки по CRC-4, используется 2-битовое сообщение Е1Е2. Каждый бит Е связан с одним из принятых сверхциклов SMF (в составе сверхцикла MFAS используется два сверхцикла SMF, поэтому сообщение использует два бита Е). Когда оборудование приемника получает информацию об ошибке CRC-4, оно генерирует бит Е для сообщения передатчику о принятой ошибке.

SMF#1 - Подцикл 1

SMF#2 - Подцикл 2

с1, с2, с3, с4 - биты CRC

001011 - сигнал сверхцикловой синхронизации CRC

Биты E1 и Е2 идентифицируют ошибку по CRC (E=1 - нет ошибки, Е=0 - ошибка по CRC)

Sn = биты, зарезервированные под задачи национального использования и для передачи управляющей информации сетевого уровня

|

Циклы передачи Е2, Е3 и Е4 формируются посредством плезиохронного побитового объединения циклов нижнего иерархического уровня (рисунок 2.4).

Циклы передачи Е2, Е3 и Е4 формируются посредством плезиохронного побитового объединения циклов нижнего иерархического уровня (рисунок 2.4). скорость и фаза записи данных в параллельные буферы может различаться, но скорость считывания этих данных из буферов одинакова;

скорость и фаза записи данных в параллельные буферы может различаться, но скорость считывания этих данных из буферов одинакова;

26) Контроль качества передачи в PDH-системах. Алгоритм цикловой синхронизации.

26) Контроль качества передачи в PDH-системах. Алгоритм цикловой синхронизации.

Мониторинг по CRC производится в режиме реального времени непосредственно после установления циклового синхронизма. В этом случае возникает цикловая синхронизация по CRC-4 и сверхциклам SMF по кодовой последовательности 001011. Эта синхронизация достаточно устойчивая, потеря цикловой синхронизации по CRC-4 отображается только после того, как более чем 914 сообщений CRC в секунду не соответствует ожидаемым значениям.

Мониторинг по CRC производится в режиме реального времени непосредственно после установления циклового синхронизма. В этом случае возникает цикловая синхронизация по CRC-4 и сверхциклам SMF по кодовой последовательности 001011. Эта синхронизация достаточно устойчивая, потеря цикловой синхронизации по CRC-4 отображается только после того, как более чем 914 сообщений CRC в секунду не соответствует ожидаемым значениям.