Принцип синхронизации и согласования скоростей приемопередающих систем PDH на иерархических уровнях E2-E3-E4.

Таблица 1 - Скоростные ряды и схемы мультиплексирования для каждой из иерархий

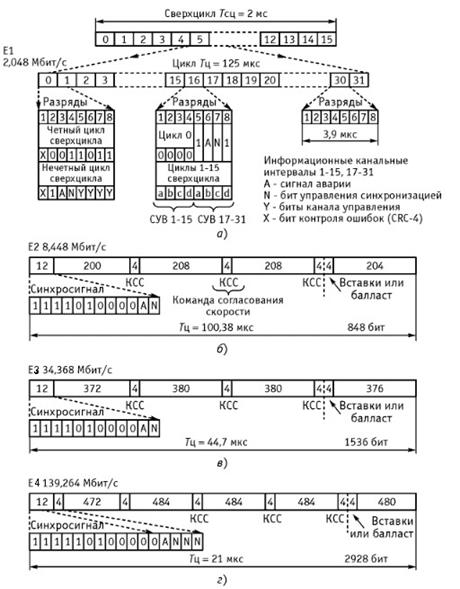

Скорости цифровых потоков одной и той же ступени иерархии, которые образованы цифровыми системами передачи, расположенными на различных узлах сети и имеющие независимые источники синхронизации, могут несколько отличаться в пределах допустимой нестабильности тактовых генераторов. Так как эта нестабильность невелика, то объединяемые потоки называют плезиохронными («почти синхронными»), а иерархию цифровых систем на основе объединения плезиохронных потоков называют плезиохронной цифровой иерархией (Plesiochronous Digital Hierarchy – PDH). Для объединения таких потоков используется схема мультиплексирования с бит-интерливингом, а для выравнивания скоростей, через несколько тысяч бит, когда расхождения накапливаются, используется либо вставка бит (стаффинг), либо исключение бит ("исключенные" биты передают в битах служебной информации). Этот процесс называется согласованием скоростей. Для того, чтобы правильно демультиплексировать такой поток, кроме синхронизирующей последовательности бит, он содержит дополнительные служебные биты в которых передается информация о согласовании скоростей. Так в канале Е2 количество служебной информации (вместе с синронизирующей последовательностью) составляет 32 бита на кадр, частота следования кадров как и у Е1 – 8 КГц, что дает результирующую скорость потока 2048х4+32х8=8448 Кбит/сек, Е3 содержит 36 бит служебной информации, но частота следования кадров у него 16 КГц, что в два раза выше, чем у Е1 или Е2, поэтому его скорость равна 8448х4+36х16=34368 Кбит/сек, у Е4 частота следования кадров 64 КГц, служебных бит 28, что дает 34368х4+28х64=139264 Кбит/сек.

Циклы передачи Е2, Е3 и Е4 формируются посредством плезиохронного побитового объединения циклов нижнего иерархического уровня (рисунок 2.4). Принцип плезиохронного мультиплексирования состоит в следующем: o объединяемые цифровые данные, имеющие различные тактовые интервалы (в известных нормативных пределах), должны быть синхронизированы, т.е. согласованы по фазе и частоте тактов; o для синхронизации объединяемых данных должен быть применен буфер памяти; o скорость и фаза записи данных в параллельные буферы может различаться, но скорость считывания этих данных из буферов одинакова; o в процессе записи данных в буфер и считывании могут образоваться в случайные моменты времени состояния неопределенности: · период записи T зап > периода считывания T cч, в этом случае буфер может дважды считаться, т.е. произойдет ложная двоичная единица; · период записи T зап < периода считывания T cч, в этом случае буфер может оказаться на момент считывания “пустым”, т.е. произойдет ложная двоичная единица.

|