Все выходные сигналы, имеющие одинаковое название собираются по принципу логического ИЛИ.

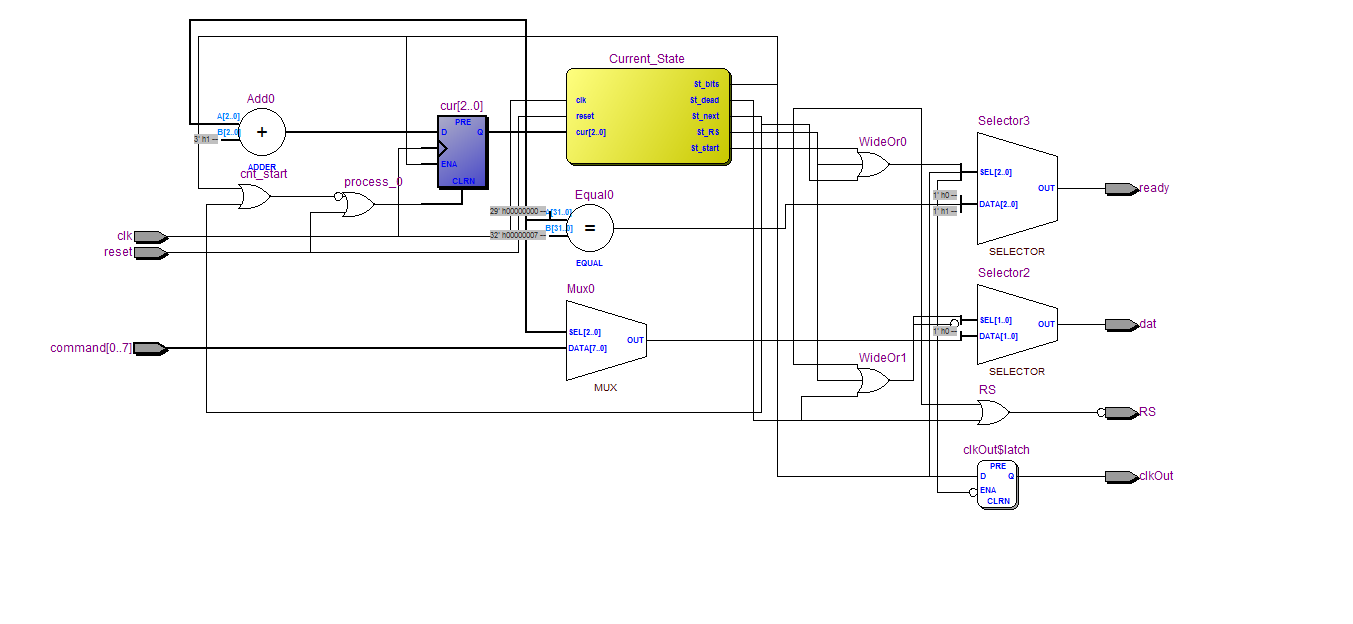

Clk подается на все компоненты. Если у управляющего компонента имя выходного сигнала совпадает с именем входного сигнала вспомогательного компонента, то первый использует второго. На VCC непрерывно подается логическая единица. На pump1 и pump2 в противофазе подаются синхросигналы с частотой 500 кГц. Разработка VHDL модулей Весь исходный код проекта представлен в приложении А в электронном виде. RTL-схема компонента

Рис 3. Схема ValueFSM

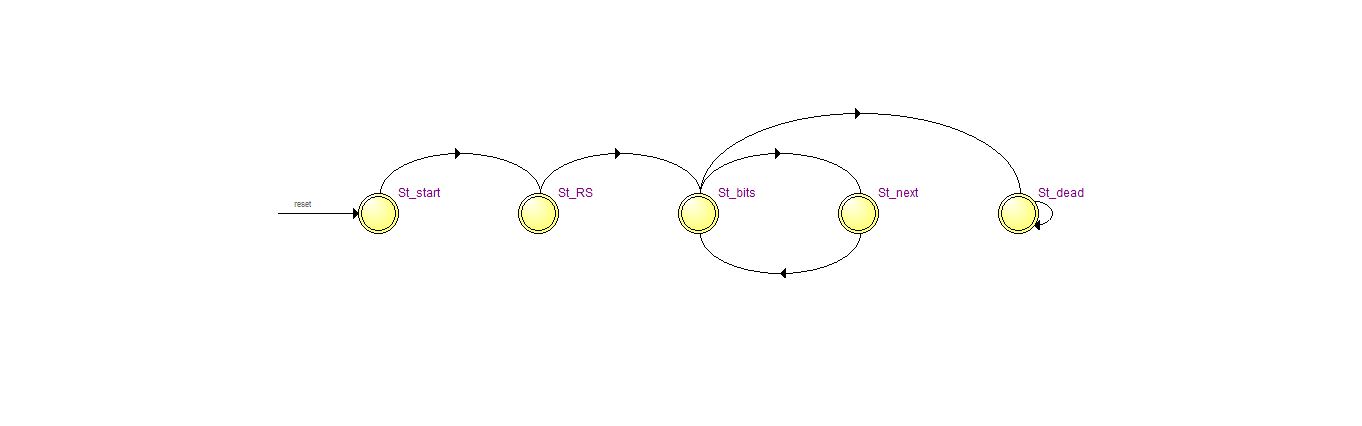

Рис 4. Конечный автомат ValueFSM

|