Двоичный сумматор

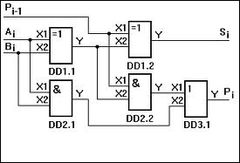

В своей простейшей форме (на рисунке № 1) сумматор имеет 4 сигнальных линии: пара входов для сигналов, представляющих одноразрядные двоичные числа "А" и "В", выход "S" (сумма "А" и "В") и сигнал переноса "M". Эта схема, которая обеспечивает складывание однобитных чисел "А" и "В", при этом "S" наименее значимый бит, "M" наиболее значимый бит, называется "полусумматор". Задействовав дополнительную схему "ИЛИ" (на рисунке зелёного цвета), можно подключить две этих "половинки" вместе (на рисунке № 2) и создать новую схему с дополнительным входом, "m", который принимает сигнал переноса старшего бита из предыдущей схемы. Такое составление двух "полусумматоров" даёт полный сумматор. Схема полного сумматора может быть использована в качестве "строительных блоков" для построения схем, путём добавления двоичных чисел с неограниченным числом бит, как показано на рисунке № 3. Для каждой цифры, которую схема должна быть в состоянии обрабатывать, используется один полный сумматор и сигнал переноса "M" от предыдущего сумматора на вход последующего. Двоичный одноразрядный полный сумматор является полной тринарной (трёхоперандной) двоичной логической функцией с бинарным (двухразрядным) выходом. Все три операнда и оба выходных разряда однобитные. Может быть построен как тринарная (трёхоперандная) двоичная функция с бинарным выходом, но, для уменьшения аппаратных затрат, обычно строится трёхступенчатым, состоящим из трёх узлов: двух полусумматоров, которые являются полными бинарными (двухоперандными) двоичными логическими функциями с унарным выходом и логического элемента «2ИЛИ».

|