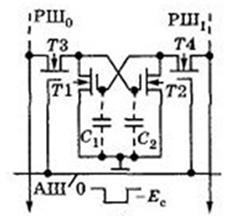

Динамическая ЗЯ на однотипных МОП-транзисторах.

Хранение бита информации осуществляется емкостями C1 и С2. Методика записи и считывания — та же, что и в предыдущей ячейке. Пусть при записи на разрядные шины РШ1 и РШ0 поданы соответственно уровни –Ес и 0. Уровень –Ес через ключ T4 поступит на затвор транзистора Т1, и этот транзистор будет открыт. На затвор транзистора Т2 поступит уровень 0, и этот транзистор будет заперт. Напряжения на емкостях будут иметь значения Uc1 = – Ес, UC2 = 0. Если остаточный ток запертого транзистора Т2 достаточно мал, то емкость C1 будет разряжаться весьма медленно и, следовательно, напряжения –ЕС и 0 будут сохраняться на выходах ячейки (на стоках) длительное время. За это время можно несколько раз считывать информацию из ячейки (хотя при считывании емкость дополнительно шунтируется цепями считывания и ее разряд ускоряется). Для того чтобы поддерживать напряжение на емкости, несмотря на неизбежный ее разряд, осуществляют регенерацию (периодическая запись того же кода). Динамические ЗЯ значительно экономичнее статических, так как у них отсутствует источник питания и, следовательно, в режиме хранения они не потребляют мощность.

ЗЯ на многоэмиттерных БПТ. Принципы записи и считывания здесь такие же, как и в предыдущих ЗУ, если не считать положительных полярностей логических уровней и адресного (тактового) импульса. Пусть в режиме хранения транзистор Т2 заперт, а Т1 насыщен, тогда Uб1 = U* и Uб2 ≈ 0. Если на разрядных шинах задан небольшой (0,1–0,2 В) «дежурный» потенциал, то эмиттерный переход Э21 будет практически заперт и весь ток будет проходить через Э11; в транзисторе Т2 будут заперты оба эмиттерных перехода. При считывании, когда на адресную шину подается положительное напряжение Ек, эмиттер Э11 запирается и ток транзистора Т 1 протекает в шину РШ0 через эмиттер Э21, который остался под низким потенциалом; шина РШ1 остается обесточенной. При записи одновременно с адресным импульсом подается напряжение +ЕК на ту разрядную шину, которая связана с транзистором, подлежащим запиранию. В нашем примере, если подать напряжение Ек на шину РШ1, то транзистор Т 2 останется запертым и состояние ЗЯ не изменится. Если же подать напряжение Ек на шину РШ0, то окажутся запертыми оба эмиттера транзистора Т1. Тогда ток потечет через базу транзистора Т2 в эмиттер Э22, который находится под низким потенциалом шины РШ1. При этом транзистор Т2 откроется, т. е. состояние ЗЯ изменится на обратное.

Основные параметры ОЗУ: • Информационная емкость ОЗУ в битах — параметр, характеризующий степень интеграции элементов на кристалле. • Удельная мощность ОЗУ, т. е. общая мощность, потребляемая в режиме хранения, отнесенная к 1 биту. • Минимальный период обращения (Тобр мин) — минимально допустимый интервал между началом одного цикла считывания и началом второго. Величина, обратная Тобр мин, называется максимальной частотой обращения. При записи оба эти параметра могут быть несколько иными. • Удельная стоимость одного бита информации, т. е. общая стоимость кристалла, поделенная на информационную емкость. Этот параметр — один из решающих при сравнительных оценках. MOП-транзисторные ОЗУ в целом превышают биполярные по информационной емкости, удельной мощности и удельной стоимости, но значительно уступают по быстродействию. Особое место среди биполярных ОЗУ занимают схемы в базисе И2Л, которые по емкости и удельной мощности приближаются к МОП-транзисторным. Среди последних минимальная удельная мощность свойственна КМОП-схемам, а минимальная стоимость — динамическим типам ОЗУ. Среди биполярных разновидностей максимальным быстродействием характерны ОЗУ в базисе ЭСЛ.

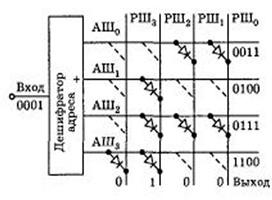

Типичная схема диодного ПЗУ показана на рисунке. Структура схемы матричная; строки образуются адресными шинами, а столбцы — разрядными. Каждая адресная шина хранит определенный код: 0011, 0100 и т. д. Запись кода (в принципе — однократная) осуществляется с помощью диодов, которые присоединены между адресными шинами и теми разрядными шинами, на которых (при считывании) должна быть логическая 1.

Типичная схема диодного ПЗУ показана на рисунке. Структура схемы матричная; строки образуются адресными шинами, а столбцы — разрядными. Диоды изготавливают во всех узлах матрицы и в таком однородном виде матрицу поставляют заказчику. Каждый заказчик сам записывает в ПЗУ нужные ему коды. Для этого он (с помощью специальных устройств) пережигает выводы — перемычки тех диодов, которые находятся в местах расположения логических нулей. Такие диоды с перегоревшими выводами показаны на рисунке штриховыми линиями.

|