Параллельные регистры

Цель работы Изучить режимы работы параллельного регистра. Краткие теоретические сведения Регистр — последовательное логическое устройство, используемое для хранения n-разрядных двоичных слов (чисел) и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств. Основой построения регистров являются D-триггеры, RS-триггеры. По типу приёма и выдачи информации различают 3 типа регистров: 1) с последовательным приёмом и выдачей информации — сдвиговые регистры 2) с параллельным приёмом и выдачей информации — параллельные регистры 3) с параллельно-последовательным приёмом и выдачей информации Параллельные регистры Параллельные регистры – это устройства, предназначенные для записи, хранения и выдачи информации, представленной в виде двоичных кодов.

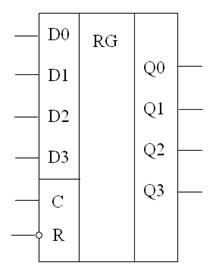

Рис. 2.1 Четырехразрядный параллельный регистр

Рис. 2.2 УГО параллельного регистра

Рис. 2.3 УГО регистра К555ИР15

Для хранения каждого двоичного разряда в регистре используется она триггерная ячейка. Для запоминания многоразрядных слов необходимое число триггеров объединяют вместе и рассматривают как единый функциональный узел – регистр. Если регистр построен на триггерах-защелках, то его называют регистр-защелка. Типовыми внешними связями регистра являются информационные входы D0-Dn, вход сигнала записи (или загрузки) С, вход сброса R и выходы триггеров: прямые Q0-Qn и инверсные Q0-Qn. В упрощенном варианте регистр может не иметь входа сброса и инверсных входов. В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, то есть цепи управления. Пример схемы статического регистра, построенного на триггерах типа D с прямыми динамическими входами, имеющего входы сброса и выходы с третьим состоянием, управляемые сигналом EZ.

|