Иерархическая организация и сравнительные характеристики устройств памяти

Для фон-Неймановских ЭВМ память часто называют «узким местом» из-за постоянного отставания по быстродействию от процессоров. К тому же, чем меньше время доступа, тем выше стоимость устройства памяти. Требования к увеличению емкости и быстродействия памяти, снижению времени доступа, а также к снижению ее стоимости являются противоречивыми. Чем больше быстродействие, тем технически труднее достигается и дороже обходится увеличение емкости памяти. Стоимость памяти составляет значительную часть общей стоимости ЭВМ. Исходя из этого, память ЭВМ организуется в виде иерархической структуры запоминающих устройств, обладающих различным быстродействием и емкостью. Чем выше уровень, тем выше быстродействие соответствующей памяти, но меньше её емкость. Система управления памятью обеспечивает обмен информационными блоками между уровнями, причем обычно первое обращение к блоку информации вызывает его перемещение с низкого медленного уровня на более высокий. Это позволяет при последующих обращениях к данному блоку осуществлять его выборку с более быстродействующего уровня памяти.

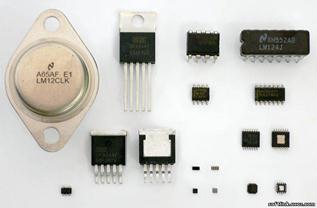

Оперативная память может составляться из микросхем динамического (Dynamic Random Access Memory — DRAM) или статического (Static Random Access Memory — SRAM) типа. Память статического типа обладает существенно более высоким быстродействием, но значительно дороже DRAM. В статической памяти элементы (ячейки) построены на различных вариантах триггеров — схем с двумя устойчивыми состояниями. После записи бита в такую ячейку она может пребывать в этом состоянии сколь угодно долго — необходимо только наличие питания. При обращении к микросхеме статической памяти на нее подается полный адрес, который при помощи внутреннего дешифратора преобразуется в сигналы выборки конкретных ячеек. Ячейки SRAM имеют малое время срабатывания (единицы наносекунд), однако микросхемы на их основе отличаются низкой удельной емкостью (единицы Мбит на корпус) и высоким энергопотреблением. Поэтому статическая память используется в основном в качестве микропроцессорной и буферной (кэш-память). В динамической памяти ячейки построены на основе полупроводниковых областей с накоплением зарядов — своеобразных конденсаторов, — занимающих гораздо меньшую площадь, нежели триггеры, и практически не потребляющих энергии при хранении. Конденсаторы расположены на пересечении вертикальных и горизонтальных шин матрицы; запись и считывание информации осуществляется подачей электрических импульсов по тем шинам матрицы, которые соединены с элементами, принадлежащими выбранной ячейке памяти. При обращении к микросхеме на ее входы вначале подается адрес строки матрицы, сопровождаемый сигналом RAS (Row Address Strobe — строб адреса строки), затем через некоторое время — адрес столбца, сопровождаемый сигналом С AS (Column Address Strobe — строб адреса столбца). Поскольку конденсаторы постепенно разряжаются (заряд сохраняется в ячейке в течение нескольких миллисекунд), во избежание потери хранимой информации заряд в них необходимо постоянно регенерировать, отсюда и название памяти — динамическая. На подзаряд тратится и энергия, и время, и это снижает производительность системы. Ячейки динамической памяти по сравнению со статической имеют большее время срабатывания (десятки наносекунд), но большую удельную плотность (порядка десятков Мбит на корпус) и меньшее энергопотребление. Динамическая память используется для построения оперативных запоминающих устройств основной памяти ПК.

|

Сравнительно небольшая емкость оперативной памяти компенсируется практически неограниченной емкостью внешних запоминающих устройств. Однако эти устройства значительно более медленные. Исходя из этого, вычислительный процесс должен протекать с возможно меньшим числом обращений к внешней памяти.

Сравнительно небольшая емкость оперативной памяти компенсируется практически неограниченной емкостью внешних запоминающих устройств. Однако эти устройства значительно более медленные. Исходя из этого, вычислительный процесс должен протекать с возможно меньшим числом обращений к внешней памяти.