Физическая структура основной памяти

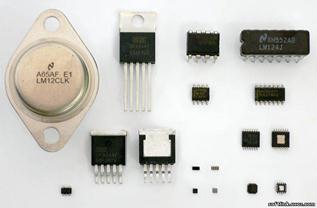

Упрощенная структурная схема модуля основной памяти при матричной его организации представлена на рис. 6.1. При матричной организации адрес ячейки, поступающий в регистр адреса, например по 20-разрядным кодовым шинам адреса, делится на две 10-разрядные части, поступающие соответственно в Рег. адр. X и Рег. адр. Y. Из этих регистров коды полуадресов поступают в дешифраторы дешифратор X и дешифратор Y,каждый из которых в соответствии с полученным адресом выбирает одну из 1024 шин. По выбранным шинам подаются сигналы записи-считывания в ячейку памяти, находящуюся на пересечении этих шин. Таким образом адресуется 106 (точнее 10242) ячеек. Считываемая или записываемая информация поступает в регистр данных (Рег. данных), непосредственно связанный с кодовыми шинами данных. Управляющие сигналы, определяющие, какую операцию следует выполнить, поступают по кодовым шинам инструкций. Куб памяти содержит набор запоминающих элементов — собственно ячеек памяти. Основная память (ОП) содержит оперативное (RAM — Random Access Memory) и постоянное (ROM — Read Only Memory) запоминающие устройства. Оперативное запоминающее устройство (ОЗУ) предназначено для хранения информации (программ и данных), непосредственно участвующей в вычислительном процессе в текущий интервал времени. ОЗУ — энергозависимая память: при отключении напряжения питания информация, хранящаяся в ней, теряется. Основу ОЗУ составляют микросхемы динамической памяти DRAM. Это большие интегральные схемы, содержащие матрицы полупроводниковых запоминающих элементов — полупроводниковых конденсаторов. Наличие заряда в конденсаторе обычно означает «1», отсутствие заряда — «0». Конструктивно элементы one На логическом уровне память представляет собой совокупность ячеек определённой разрядности (в настоящее время, как правило, 1 байт), к содержимому которых можно обращаться (по чтению или по записи) путём указания их адресов. ОП ПЭВМ состоит из одного или нескольких устройств памяти. Устройства памяти характеризуются следующими основными показателями: 1) временем доступа (быстродействием); 2) емкостью; 3) стоимостью; 4) потребляемой мощностью (энергопотреблением). Время доступа – это промежуток времени, за который может быть записано или прочитано содержимое ячейки памяти после подачи её адреса и соответствующего управляющего сигнала. Ёмкость определяет количество ячеек или битов в устройстве памяти. Однако этим показателем ёмкость ОП ПЭВМ не ограничивается, так как она может содержать несколько устройств памяти. Стоимость измеряется денежными затратами в расчете на единицу ёмкости памяти. Классификация устройств ОП ПЭВМ по функциональному признаку предоставлена на рис. 2.4. все устройства памяти базируются на полупроводниковой технологии и выполняются в виде ИМС. В связи с этим показатель «ёмкость» сводится по пути к удельной ёмкости (количеству ячеек или битов на кристалле).

Рис. 2.4. Устройства основной памяти В аналогичной литературе вместо ОЗУ используется термин RAM (Random-Access Memory – запоминающее устройство с произвольной выборкой – ЗУПВ). Под произвольностью выборки в данном случае понимают возможность непосредственного доступа к любой (произвольной) заданной ячейке памяти, причем время доступа для любой ячейки одинаково. Но термин ЗУПВ ничего не говорит о функциональных возможностях, а именно о том, что оно используется в качестве временной рабочей памяти машины, обеспечивая как запись, так и считывание информации (программ и данных). В зависимости от способа хранения информации ОЗУ подразделяют на: 1) статические ОЗУ (SRAM – Static RAM): 2) динамические ОЗУ – (DRAM – Dynamic RAM); 3) статические векторные ОЗУ (SCRAM – Static-Column RAM); 4) псевдостатические ОЗУ (P-SRAM – Pseudo-Static RAM). В SRAM каждый бит информации (1 или 0) хранится на элементе типа электронной защелки (обобщение триггера), состояние которого остаётся неизменным до тех пор, пока не будет сделана новая запись в этот элемент или не будет выключено питание.

|