ИССЛЕДОВАНИЕ КОМБИНАЦИОННЫХ УСТРОЙСТВ

Комбинационными называются функциональные узлы, которые построены только на логических элементах и не содержат элементов памяти. Иначе их называют автоматы с нулевой памятью. Состояние комбинационного узла однозначно определяется входным сигналом и не зависит от предыдущего состояния.

3.1ИССЛЕДОВАНИЕЛОГИЧЕСКИХ ФУНКЦИЙ «ИСКЛЮЧАЮЩЕЕ ИЛИ» И ЕЁИНВЕРСИИ

Сумматор по модулю «2» в случае наличия только двух входов выполняет функцию логического элемента «Исключающее ИЛИ». Фактически получается узел неравнозначности, т.е. сигнал на выходе равен «1» только при несовпадении значений входных сигналов. y=a Преобразуем последнее выражение по теореме де Моргана. y= Coответствующий этой структурной формуле схемотехнический вариант в базисе И-НЕ показан на рис.3.1.

Для функции

Схематическое решение в базисе И-НЕ представлено на рис.3.2.

Рис.3.2 Реализация функции

Дополнительно те же функции можно исследовать на схемах, представленных на рис.3.3, а,б. В лабораторной работе необходимо построить по указанию преподавателя некоторые схемы для реализации рассматриваемых функций и получить для них таблицы истинности, задавая различные двоичные входные сигналы.

a

Рис.3.3Варианты исполнения функций:а) Контрольные вопросы 1. Написать основные формулы булевой алгебры. 2. Объяснить, что означают термины «позитивная логика» и «негативная логика». 3. Написать таблицы истинности для функций y=a 4. Пояснить смысл термина «Исключающее ИЛИ». 5. Объяснить, что означает термин «нормальная дизъюнктивная форма» записи логических переменных.

3.2ПОСТРОЕНИЕ СХЕМЫ МУЛЬТИПЛЕКСОРА НА ДВА ВХОДА Мультиплексор (МХ) – управляемый кодом коммутатор нескольких входов на один выход. МХ содержит две группы входов – информационные и управляющие. С выходом соединяется тот входной сигнал, индекс которого, записанный в двоичной форме, совпадает с управляющим кодом. В случае четырёх входных каналов достаточно иметь два разряда в управляющем двоичном коде. Соответствующая структурная формула может быть записана в виде: y= Для случая двух входов МХ реализует функциюy= Используя аксиомы алгебры логики и теорему де Моргана, эту функцию можно преобразовать к виду:y =

3.3ПОСТРОЕНИЕ СХЕМЫ ЦИФРОВОГО КОМПАРАТОРА

Цифровой компаратор предназначен для сравнения двух многоразрядных двоичных чисел. В простейшем случае требуется лишь установить факт равенства числа А и В. Для этого производится поразрядное тестирование чисел А и В с помощью, например функции равнозначности y= Преобразуем выражение для функции равнозначности с помощью теоремы де Моргана.y= аb + В результате получаем схему компаратора, показанную на рис.3.5.Необходимо собрать эту схему и проверить её работоспособность.

6 t3qtKvN49bJ7M89h2nxIeXkxP9wDizjHPxh+9UkdCnKq/dHpwHoJN8lyQygFgiYQcJuINbBawjpd AS9y/n9B8QMAAP//AwBQSwECLQAUAAYACAAAACEAtoM4kv4AAADhAQAAEwAAAAAAAAAAAAAAAAAA AAAAW0NvbnRlbnRfVHlwZXNdLnhtbFBLAQItABQABgAIAAAAIQA4/SH/1gAAAJQBAAALAAAAAAAA AAAAAAAAAC8BAABfcmVscy8ucmVsc1BLAQItABQABgAIAAAAIQBIST5q/wEAAAcEAAAOAAAAAAAA AAAAAAAAAC4CAABkcnMvZTJvRG9jLnhtbFBLAQItABQABgAIAAAAIQCxjIBO4AAAAAkBAAAPAAAA AAAAAAAAAAAAAFkEAABkcnMvZG93bnJldi54bWxQSwUGAAAAAAQABADzAAAAZgUAAAAA " strokecolor="black [3040]">

Контрольные вопросы

1. Как производится сравнение двоичных чисел? Сравните числа 1011 и 1001, используя предложенный алгоритм. 2. Как сравниваются два одноразрядных числа? 3. Как можно сравнивать двоично-десятичные числа? 4. Показать, как могут соединяться компараторы типа К555СП1 при увеличении разрядности сравниваемых чисел.

3.4 ОПИСАНИЕ ЛАБОРАТОРНОЙ УСТАНОВКИ

См. разд. 1.5 лабораторной работы №1 «Исследование счётчиков на интегральных элементах».

3.5ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

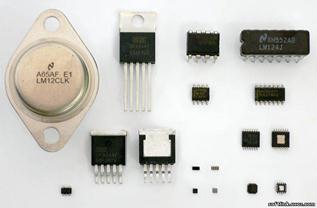

1. Собрать на выключенном макете схемы по указанию преподавателя из перечня «Исключающее ИЛИ» и её инверсное значение, мультиплексор, компаратор. При этом нужно руководствоваться схемами на рис 3.1 – 3.5. Для реализации устройств обычно достаточно логических микросхем макета, обозначенных номерами 6,11,12,13,14,20,21. 2. Исследовать работу устройства, варьируя комбинации входных сигналов. 3. Представить результаты работы в виде таблицы истинности и показать её преподавателю. 4. Выключить макет и разобрать схему соединений.

3.6СОДЕРЖАНИЕ ОТЧЁТА

Отчёт должен содержать (в соответствии с выполненным заданием на работу): - схему исследуемого устройства; - теоритическое обоснование; - таблицу состояний устройства; - выводы по проделанной работе

3.7ТРЕБОВАНИЯ БЕЗОПАСНОСТИ

Смотри раздел 1.8 лабораторной работы №1 «Исследование счётчиков на интегральных элементах»

|

b =

b =

=

=

b

b

сигнал на выходе равен «1» при двух одинаковых входных сигналах.

сигнал на выходе равен «1» при двух одинаковых входных сигналах. = ab+

= ab+  =

=  =

=  .

. в базисе И - НЕ

в базисе И - НЕ

b

b

b и у=a

b и у=a

+a1

+a1  0 x2 +

0 x2 +  .

. .

. =

=  =

=  .В работе требуется построить схему МХ на логических элементах 2И-НЕ (рис.3.4) и проверить её функционирование

.В работе требуется построить схему МХ на логических элементах 2И-НЕ (рис.3.4) и проверить её функционирование = аb +

= аb +  . Число сумматоров должно быть равно разрядности чисел. Выходы сумматоров подключаются к схеме И. Только при совпадении значений всех разрядов чисел А и В на выходе будет «1». Для установления знака неравенства А>В или А<В, используют специальные тестовые схемы, начиная со старших разрядов. Ограничим рассмотрение одноразрядным случаем для построения компаратора в базисе 2И-НЕ.

. Число сумматоров должно быть равно разрядности чисел. Выходы сумматоров подключаются к схеме И. Только при совпадении значений всех разрядов чисел А и В на выходе будет «1». Для установления знака неравенства А>В или А<В, используют специальные тестовые схемы, начиная со старших разрядов. Ограничим рассмотрение одноразрядным случаем для построения компаратора в базисе 2И-НЕ. =

=  .

.