Регистры

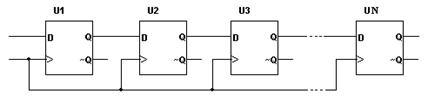

В последовательном регистре выход предыдущего триггера подается на вход следующего триггера, а тактовые импульсы подаются на входы С всех триггеров, составляющих регистр, одновременно (рис. 6.34). При этом содержимое каждого триггера записывается в последующий триггер. Такие регистры называются сдвиговыми регистрами, или регистрами сдвига.

Рис. 6.34. Последовательный регистр (регистр сдвига)

Рис. 6.35. Моделирование последовательного регистра в Multisim Если на вход D регистра сдвига подать единицу, а на вход С тактовую частоту, то единица начнет продвигаться по регистру сдвига, т.е. под воздействием первого тактового импульса единица запишется в первый триггер регистра. Под воздействием второго тактового импульса эта единица перепишется во второй триггер и т.д., когда под воздействием N -го тактового импульса единица не выйдет из регистра сдвига. Временная диаграмма работы четырехразрядного регистра сдвига приведена на рис. 6.36.

Рис. 6.36. Временная диаграмма четырехразрядного регистра сдвига Виды регистров сдвига: · с последовательным вводом и выводом; · с последовательным вводом и параллельным выводом; · с параллельным вводом и последовательным выводом; · Кроме последовательных регистров сдвига существуют параллельные регистры, в

Рис. 6.38. Моделирование параллельного регистра в Multisim Параллельные регистры используются для хранения двоичной информации небольшого объема в течение короткого промежутка времени.

Счетчиком называется устройство, подсчитывающее число входных импульсов. Число, представляемое состоянием его выходов по фронту каждого входного импульса, изменяется на единицу. Счетчик состоит из n последовательно соединенных счетных триггеров, причем выход одного счетного триггера соединен с тактовым входом следующего триггера. Счетчики бывают суммирующими (прямой счет) и вычитающими (обратный счет). В суммирующих счетчиках каждый входной импульс увеличивает число на его выходах на единицу, в вычитающих счетчиках уменьшает это число на единицу. Для того чтобы построить суммирующий счетчик, необходимо счетный вход очередного триггера подключить к инверсному выходу предыдущего (рис. 6.39).

Рис. 6.39. Суммирующий счетчик и диаграмма его работы

Рис. 6.40. Моделирование суммирующего счетчика в Multisim

Для того чтобы изменить направление счета (реализовать вычитающий счетчик), необходимо счетный вход очередного триггера подключить к прямому выходу предыдущего, при этом изменяется последовательность переключения триггеров (рис. 6.41). Счетчик характеризуется числом состояний в течение одного периода (цикла). Для двоичных счетчиков полный цикл счета N =2 n от состояния 0..000 до состояния 1…11. Число состояний называется коэффициентом пересчета K сч, равным отношению числа импульсов Nс на входе к числу импульсов NQ ст на выходе старшего разряда за период:

Рис. 6.41. Вычитающий счетчик и диаграмма его работы

Рис. 6.42. Моделирование вычитающего счетчика в Multisim Счетчик характеризуется числом состояний в течение одного периода (цикла). Для двоичных счетчиков полный цикл счета N =2 n от состояния 0..000 до состояния 1…11. Число состояний называется коэффициентом пересчета K сч, равным отношению числа импульсов Nс на входе к числу импульсов NQ ст на выходе старшего разряда за период:

Если на вход счетчика подавать периодическую последовательность импульсов с частотой fс, то частота fQ на выходе старшего разряда счетчика будет меньше в K сч раз: K сч= fс / fQ. Поэтому счетчики также называют делителями частоты, а K сч – коэффициентом деления. Для увеличения величины K сч нужно увеличить число триггеров в цепочке. Каждый дополнительный триггер удваивает число состояний счетчика и число K сч.

Комбинационной называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов. Дешифратор – логическая комбинационная схема, имеющая n информационных входов и 2 n выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из 2 n выходов. Как любая логическая схема, дешифратор может быть задан таблицей истинности. Таблица истинности дешифратора 3х8 (табл. 6.3) состоит из трех столбцов, соответствующих входным сигналам Х 0, Х 1, Х 2, и восьми столбцов, соответствующих выходным сигналам Y 0, Y 1, Y 2, Y 3, Y 4, Y 5, Y 6, Y 7. В первых слева трех столбцах расположены возможные комбинации входных сигналов, а в последних восьми – соответствующие им комбинации выходных сигналов. Т а б л и ц а 6.3

Схема имеет восемь выходов, на одном из которых потенциал высокий, на остальных низкий. Номер единственного выхода, имеющего высокий потенциал, соответствует двоичному числу, формируемому состояниями входных сигналов. Этот принцип формирования выходного сигнала можно описать следующим образом: Yi = 0, если i = k; Yi = 1, если i ≠ k, здесь i – номер разряда; k = 22 X 2 + 21 X 1 + 20 X 0.

Выражения для каждого выхода дешифратора:

где «¯» – инвертирование. Таким образом, схема дешифратора должна содержать три схемы «НЕ» и восемь схем «3И» (рис. 6.43).

Рис. 6.43. Схема дешифратора 3х8

Рис. 6.44. Моделирование дешифратора 3х8 в Multisim

|

Триггерным регистром называется совокупность триггеров с определенными связями между ними, при которых они действуют как единое устройство. Регистры выполняются на синхронных триггерах JK - или D -типа. В зависимости от выполняемых функций регистры делятся на накопительные (параллельные) и сдвигающие.

Триггерным регистром называется совокупность триггеров с определенными связями между ними, при которых они действуют как единое устройство. Регистры выполняются на синхронных триггерах JK - или D -типа. В зависимости от выполняемых функций регистры делятся на накопительные (параллельные) и сдвигающие.

с переменным направлением сдвига (реверсивные регистры сдвига).

с переменным направлением сдвига (реверсивные регистры сдвига).

Счетчики.

Счетчики.

.

.

Дешифраторы.

Дешифраторы.