Достоинствами ИМС КМОП являются малая потребляемая мощность и высокая помехозащищенность в сочетании с высоким быстродействием и нагрузочной

: способностью. Питание таких ИМС производится от источника напряжения +5...+15В. Разработка первых ИМС КМОП серии CD4000 была выполнена фирмой RCA в 1968 г. Позднее эта фирма выпустила еще две серии усовершенствованных ИМС CD4000A и CD4000B. Основные серии ИМС КМОП, их отечественные аналоги и фирмы-разработчики приведены в табл. 12.5. По сравнению с ИМС ТТЛ микросхемы КМОП имеют следующие достоинства: • малая потребляемая мощность в диапазоне частот до 2 МГц (мощность в статическом режиме не превышает 1 мкВт); • большой диапазоне напряжений питания (от 3 до 15 В); • очень высокое входное сопротивление (больше 1 МОм); • большая нагрузочная способность (коэффициент разветвления больше 50). К недостаткам ИМС КМОП относятся: • большие времена задержки (др 100нс); Таблице! 12.6 Основные параметры ИМС КМОП

• повышенное выходное сопротивление (до 1 кОм); • значительный разброс всех параметров. Уровни выходных сигналов зависят от напряжения питания. Уровень логической «I» равен примерно 0,8Д'пит» а уровень логического «О» — от 0,3 до 2,5В. Основные характеристики различных серий ИМС КМОП приведены в табл. 12.6. Совершенствование технологии ИМС КМОП привело в настоящее время к тому, что характеристики наиболее быстродействующих ИМС КМОП серии 54НС практически сравнялись с характеристиками ИМС ТТЛ серии SN74LS. Лекция 13. Триггеры Основные сведения. Триггерами называют большой класс электронных устройств, обладающих способностью длительно находиться в одном из двух или более устойчивых состояний и чередовать их под воздействием внешних сигналов. В отличие от комбинационных логических схем, триггеры — это логические устройства с памятью. Их выходные сигналы в общем случае зависят не только от сигналов, приложенных к входам в данный момент времени, но и от сигналов, воздействовавших на них ранее. В зависимости от свойств, числа и назначения входов триггеры можно разделить на несколько видов. Виды триггеров. Триггер Г(рис. 13.1) можно представить в общем случае как устройство, состоящее из ячейки памяти ЯП и логического устройства ЛУ управления, преобразующего входную информацию в комбинацию сигналов, под воздействием которых ЯП принимает одно из двух устойчивых состояний. Информационные сигналы поступают на входы А и В ЛУ и преобразуются в сигналы, поступающие на внутренние входы S' и R' ЯП. Процесс преобразования информационных сигналов осуществляется при воздействии сигналов, подаваемых на вход Т предустановки и вход С синхронизации. Вход Т обычно используется для разрешения приема информации, а исполнительный вход С обеспечивает тактируемый прием информации. В простейшем триггере ЛУ может отсутствовать, а информационные сигналы подаются непосредственно на входы S и R ЯП. При наличии входа С триггер называют синхронным, а при его отсутствии — асинхронным. Изменение состояния асин-

Рис. 13.1. Обобщенное устройство триггера хронного триггера происходит сразу же после соответствующего изменения потенциалов на его информационных входах А и В. В синхронном триггере изменение состояния может произойти только в момент присутствия соответствующего сигнала на входе С. Синхронизация может осуществляться импульсом (потенциалом) или фронтом (перепадом потенциала) В первом случае сигналы на информационных входах оказывают влияние на состояние триггера только при разрешающем потенциале на входе С. Во втором случае воздействие информационных сигналов проявляется только в момент изменения потенциала на входе С, т е. при переходе его от 1 к 0 или от 0 к 1. Универсальные триггеры могут работать как в синхронном, так и в асинхронном режимах Основные типы триггеров в интегральном исполнении получили следующие названия, ^-триггер,./^-триггер, ^-триггер, Г-триггер. SR-триггер имеет два информационных входа S и R. Подача на вход >S' сигнала 1, а на вход R сигнала 0 устанавливает на выходе Q триггера сигнал 1. Наоборот, при сигналах S=0 и R=l сигнал на выходе триггера 6=0. Функционирование 57?-триггера определяется уравнениями.

Для SR -триггера комбинация S=l и R=l является запрещенной После такой комбинации информационных сигналов состояние триггера будет неопределенным на его выходе Q может быть 0 или 1. Существуют разновидности.УТг-триггеров, называемые Е-, R- и.У-триггерами, для которых сочетание S=R=l не является запрещенным. Я-триггер при S=R=l не изменяет своего состояния (Qn^Qn-i) ^-триггер при S^R^l устанавливается в состояние 6=1, а 7?-триггер в этом случае устанавливается в состояние 6=0. ^-триггеры могут быть асинхронными или синхронными (в этом случае у них имеется вход С). JK-триггер имеет также два информационных входа J и К Подобно ^-триггеру, в JK-триггере J и К - это входы установки выхода Q триггера в состояние 1 или 0. Однако, в отличие от ^-триггера, в ^-триггере наличие J=K= 1 приводит к переходу выхода Q триггера в противоположное состояние./.^-триггеры синхронизируются только перепадом потенциала на входе С. Условие функционирования /ЛГ-триггера имеет вид Qn=(•fQ+KQ)^. D-триггер, или триггер задержки, при поступлении синхросигнала на вход С устанавливается в состояние, соответствующее потенциалу на входе D Уравнение функционирования Д-триггера имеет вид бд=Д„,1 Это уравнение показывает, что выходной сигнал Qn изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, т е. с задержкой на один период импульсов синхронизации (Delay — задержка) Синхронизация Д-триггера может осуществляться импульсом или фронтом. Т-триггер, или счетный триггер, изменяет состояние выхода по фронту импульса на входе С Кроме синхровхода С 7-триггер может иметь подготовительный вход Т. Сигнал на этом входе разрешает (при Т= 1) или запрещает (при Г=0) срабатывание триггера от фронтов импульсов на входе С. Функционирование Г-триггера определяется уравнением Qn=(QT+QT)n-^• Из этого уравнения Рис. 13.2. Асинхронный SR -триггер (а) и его условное схематическое обозначение (б) следует, что при Т= 1 соответствующий фронт сигнала на входе С переводит триггер в противоположное состояние. Частота изменения потенциала на выходе Г-триггера в два раза меньше частоты импульсов на входе С. Это свойство Г-триггера позволяет строить на их основе двоичные счетчики. Поэтому эти триггеры и называют счетными. Счетный триггер без входа Т ведет себя так же, как и Г-триггер при Г= 1. Принципы построения триггеров. Простейший асинхронный SR -триггер состоит из двух ячеек И-НЕ (или ИЛИ-НЕ), замкнутых в кольцо (рис. 13.2 а), и по существу представляет ЯП без дополнительного ЛУ. Аналогичный ^-триггер в интегральном исполнении изображен на рис. 13.26. Переключение 57?-триггеров, изображенных на рис. 13.2, производится сигналом «О», подаваемым на входы S или R. Такие простейшие триггеры входят во все типы более сложных триггеров. Простейший синхронный 57?-триггер содержит кроме ЯП еще ЛУ из двух ячеек И-НЕ (рис. 13.3 а). Аналогичный >57?-триггер в интегральном исполнении изображен на рис. 13.3 б. Переключение ^-триггеров, изображенных на рис. 13.3,

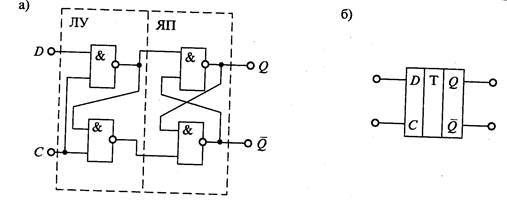

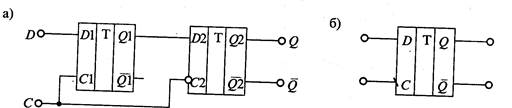

Рис. 13.3. Синхронный 57?-трИ1тер (а) и его условное схематическое обозначение (б) производится сигналом «I», подаваемым на входы S или R, или только при наличии синхросигнала С= 1. ./ЛГ-триггер выполняется по двухступенчатой структуре, состоящей из двух синхронных ^-триггеров и двух логических схем И-НЕ (рис. 13.4 а). Для этой схемы S\=JQ и R1=KQ. Если У=1 и К=0, то при Q=0 получим 5'1=1, и после окончания первого тактового импульса на входе С триггер установится в состояние 6=1. Если J=\ и К=0, то при Q=l оба входных сигнала триггера первой ступени SI и RI будут равны «О» и, соответственно, весь двухступенчатый триггер не будет изменять своего состояния при приходе синхроимпульсов на вход С Таким образом, при 7=1 и К=0 выход триггера Qn^l, если (2„-i=0 или 6„-i=l Подобным же образом по отношению к состоянию Q= 0 действует сигнал К=\ при /=0. Если же J=K=\, то получим S1=1 и R1=0 при Q=0 или S1=0 и R1=1 при 6=1. Вследствие этого при J=K=l триггер переключится в противоположное состояние при соответствующем фронте сигнала на входе С. Аналогичный /ЛГ-триггер в интегральном исполнении показан на рис. 1346. Д-триггер состоит из ЯП и ЛУ на двух ячейках И-НЕ, включенных по схеме рис 13.5 а. Д-триггер, изображенный на рис. 13.5 о, устанавливается в состояние Q=D только при С=1. Аналогичный Р-триггер в интегральном исполнении показан на рис. 13.56. Д-триггер, тактируемый фронтом, построен на двух /)-тригге-рах, тактируемых импульсом (рис. 13.6 а). На схеме рис. 13.6 а информационный вход D2 соединен с выходом QI. Синхросигнал подается на обе ступени, но в триггере второй ступени он инвертируется. Благодаря этому при любом сигнале на входе С (С=0 или С=1) один из двух триггеров не реагирует на сигнал, поступающий на его информационный вход. В результате как при С=0, так и при С= 1 изменение сигнала на входе D не приведет к непосредственному изменению выходного сигнала Q. И только в тот момент времени, когда потенциал С переходит из «I» в «О», возможно изменение сигнала Q. При С=1 триггер первой ступени воспринимает информацию со входа D. Когда же происходит изменение сигнала на входе С и он становится равным «О», производится прием информации триггером второй ступени с выхода триггера

Рис 13.4 JK-трпггер (а) и его условное схематическое обозначение (б)

Рис. 13.5. Д-триггер (а) и его условное схематическое обозначение (б) первой ступени. Переход сигнала на входе С из «I» в «О» отражен косой чертой (\) на входе С. Счетный Г-триггер можно построить на.//^-триггере или на 23-триггере. Для построения Т-триггера на.Ж-триггере нужно сделать входы J=K=l (рис. 13.7 а). Тогда каждый импульс на входе С будет изменять состояние триггера на противоположное, т. е. он превратится в Г-триггер. Для построения счетного Г-триггера на ^-триггере необходимо соединить его вход D с инверсным выходом Q, т.е. сделать D=Q (рис. 13.76). В такой схеме каждый переход 1/0 на входе С будет приводить к переходу триггера в противоположное состояние. Например, если б„=1, то @„ ==/),,= 0, и поэтому очередной тактовый импульс переведет триггер в новое состояние, т. е. сделает 6„+i=Z>„=0. Интегральные микросхемы триггеров. Промышленность выпускает большое количество интегральных микросхем триггеров, построенных на диодно-транзис-торной логике (ДТЛ), транзисторно-транзисторной логике (ТТЛ), эмиттерно-связанной логике (ЭСЛ), комплементарных полевых транзисторах (КМОП). В табл. 13.1 приведены основные типы триггеров различных серий интегральных микросхем. Условное обозначение интегральных микросхем триггеров состоит из обозначения серии (трех или четырех цифр), функционального назначения (двух букв) и порядкового номера разработки (от одной до трех цифр).

Рис. 13.6. Д-триггер, тактируемый фронтом (а), и его условное схематическое обозначение (б)

Рис. 137. Счетный Г-триггер на ТЛ^-триггере (а) и на Д-триггере (б) По функциональному назначению триггеры имеют следующие обозначения: ТР — ^-триггеры, ТВ — 7^-триггеры, ТМ — Д-триггеры, ТТ — Г-триггеры, ТП — прочие триггеры. Основные параметры интегральных микросхем триггеров можно разделить на две группы: статические и динамические. К статическим параметрам относятся: входное напряжение высокого £/'ax и низкого U^ уровней, ток потребления от источника питания, напряжение С/пит. нагрузочная способность (ток /„, отдаваемый в нагрузку, или количество Кру, микросхем той же серии, подключаемых к выходу триггера), потребляемая мощность р^[ от источника питания. К динамическим параметрам триггеров относятся, время г0-' переключения из низкого уровня в высокий, время l1 ° переключения из высокого уровня в низкий, максимальная частота /макс переключения. Большинство перечисленных параметров определяется серией микросхемы и типом применяемой логики. Интегральный триггер 155ТВ1 имеет дополнительные внешние S и R входы. Эти входы имеют приоритет по отношению к другим входам. При низком уровне S'=R=0 состояние выходов триггера неопределенное. При противоположных уровнях на S и R входах входы С, J, К не действуют. При высоком Таблица 13 1 Параметры интегральных микросхем триггеров

Таблица 13.2 Состояния триггера 555ТР2

|