Таймеры/счетчики T1 и T3

В Atmega 128 присутствует также таймеры/счетчики T1 и T3. Как и таймеры/счетчики T0 и T2, они могут использоваться для формирования временных интервалов, для подсчета числа внешних событий, формирования сигналов и генерации сигналов с ШИМ. В дополнение к этому таймеры/счетчики T1/T3 могут по внешнему сигналу сохранять свое текущее состояние в отдельном регистре ввода/вывода. В состав каждого таймера/счетчика входят следующие регистры ввода/вывода: • 16_разрядный счетный регистр TCNT1 (TCNT3); • 16_разрядный регистр захвата ICR1 (ICR3); • три 16_разрядных регистра сравнения OCR1A, OCR1B, OCR1C (OCR3A, OCR3B, OCR3C); • три 8_разрядных регистра управления TCCR1A, TCCR1B, TCCR1C (TCCR3A, TCCR3B, TCCR3C). Каждый из 16_разрядных регистров физически размещается в двух регистрах ввода/вывода, названия которых получаются добавлением к названию регистра буквы «H» (старший байт) и «L» (младший байт). Счетный регистр таймера счетчика TCNT1, например, размещается в регистрах TCNT1H:TCNT1L. Адреса всех регистров таймеров/счетчиков T1 и T3 указаны в Табл.5. 14. Таймеры/счетчики T1 и T3 могут генерировать прерывание при наступлении следующих событий: • при переполнении счетного регистра; • при равенстве счетного регистра и регистра сравнения (по одному прерыванию на каждый блок сравнения); • при сохранении счетного регистра в регистре захвата. Флаги всех прерываний таймеров/счетчиков T1 и T3 находятся в регистрах TIFR и ETIFR, а разрешение/запрещение этих прерываний осуществляется установкой/сбросом соответствующих флагов регистров TIMSK и ETIMSK Счетный регистр таймера/счетчика TCNT1 (3) входит в состав основного блока модуля — блока реверсивного счетчика. В зависимости от режима работы модуля содержимое счетного регистра сбрасывается, инкрементируется или декрементируется по каждому импульсу тактового сигнала таймера/счетчика clkT1 (clkT3). Независимо от того, присутствует тактовый сигнал или нет, регистр доступен в любой момент времени как для чтения, так и для записи. При этом любая операция записи в счетный регистр блокирует работу всех блоков сравнения на время одного периода тактового сигнала таймера/счетчика. После подачи напряжения питания в регистре TCNT1 (3) находится нулевое значение. При некоторых изменениях состояния таймера/счетчика, определяемых режимом его работы, устанавливается флаг TOV1 (3) регистра TIFR. Разрешение преры вания осуществляется установкой в «1» разряда TOIE1 (3) регистра TIMSK. Регистры OCR1A/OCR1B/OCR1C (OCR3A/OCR3B/OCR3C) входят в состав блоков сравнения. Во время работы таймера/счетчика производится непрерывное (в каждом машинном цикле) сравнение этих регистров с регистром TCNT1 (TCNT3). В случае равенства содержимого регистра сравнения и счетного регистра в следующем машинном цикле устанавливается соответствующий флаг OCF1A/OCF1B/OCF1C (OCF3A/OCF3B/OCF3C) регистра TIFR и генерируется прерывание (если оно разрешено). Также при наступлении этого события может изменяться состояние вывода OC1A/OC1B/OC1C (OC3A/OC3B/OC3C) микроконтроллера. Чтобы таймер/счетчик мог управлять состоянием какого либо из этих выводов, он должен быть сконфигурирован как выходной (соответствующий разряд регистра DDR x должен быть установлен в «1»). Особенностью работы блока сравнения в режимах, предназначенных для формирования ШИМ сигналов, является двойная буферизация записи в регистры сравнения. Она заключается в том, что записываемое число на самом деле сохраняется в специальном буферном регистре. А изменение содержимого регистра сравнения происходит только при достижении счетчиком максимального значения. Таблица5.14. Регистры 16_разрядных таймеров/счетчиков

Регистр захвата ICR1 (ICR3) входит в состав блока захвата, назначение которого — сохранение в определенный момент времени состояния таймера/счетчика в регистре захвата ICR1 (ICR3). Это действие может производиться либо по активному фронту сигнала на выводе ICP1 (ICP3) микроконтроллера, либо (для таймера/счетчика T1) по сигналу от аналогового компаратора. Одновременно с записью в регистр захвата устанавливается флаг ICF1 регистра TIFR (ICF3 регистра ETIFR) и генерируется запрос на прерывание. Разрешение прерывания осуществляется установкой в «1» разряда TICIE1 регистра TIMSK (TICIE3 регистра ETIMSK). Программно запись в регистр ICR1 (ICR3) возможна только в режимах, в которых регистр захвата определяет модуль счета таймера/счетчика. Вывод ICR1 (ICR3) в этих режимах отключен и функция захвата, соответственно, выключена. Для управления схемой захвата используются два разряда регистра TCCR1B (TCCR3B) — ICNC1 (ICNC3) и ICES1 (ICES3). Разряд ICNC1 (ICNC3) управляет схемой подавления помех. Если этот разряд сброшен в «0», схема подавления помех выключена и захват производится по первому же активному фронту на выводе. Если же этот разряд установлен в «1», то при появлении активного фронта производится 4 выборки с частотой, равной тактовой частоте микроконтроллера. Захват будет выполнен только в том случае, если все выборки имеют уровень, соответствующий активному фронту сигнала (лог. 1 для нарастающего и лог. 0 для спадающего. Активный фронт сигнала, т. е. фронт, по которому будет выполнено сохранение содержимого счетного регистра в регистре захвата, определяется состоянием разряда ICES1 (ICES3). Если этот разряд сброшен в «0», то активным является спадающий фронт. Если разряд установлен в «1», то активным является нарастающий фронт. Для захвата по сигналу с вывода, этот вывод должен быть сконфигурирован как входной (разряд регистра DDR x, соответствующий выводу, должен быть сброшен в «0»). Если же он будет сконфигурирован как выходной, захват можно будет осуществлять программно, управляя соответствующим разрядом порта. Для управления таймером/счетчиком используются три регистра управления: TCCR1A (TCCR3A), TCCR1B (TCCR3B), TCCR1C (TCCR3C).Формат этих регистров приведен на Рис. 5.12…5.14, а описание их разря_ дов — в Табл. 5.15…5,17.

Рис.5.12. Формат регистров TCCR1A (а) и TCCR3A (б)

Таблица5.15. Разряды регистра TCCR1A (TCCR3A)

Примечание: n = 1 или 3; x = A, B или C.

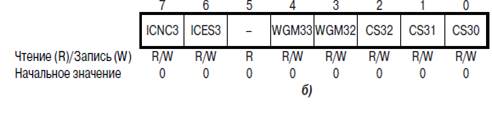

Рис.5.13. Формат регистров TCCR1B (а) и TCCR3B (б)

Таблица 5.16. Разряды регистра TCCR1B (TCCR3B)

Примечание: n = 1 или 3.

Рис.5.14. Формат регистров TCCR1C (а) и TCCR3C (б)

Таблица 5.17. Разряды регистра TCCR1C (TCCR3C)

Примечание: n = 1 или 3; x = A, B или C.

|