Цель работы. Изучение принципов работы шифраторов (CD), дешифраторов (DC), мультиплексоров (MX), демультиплексоров (DMX)

Изучение принципов работы шифраторов (CD), дешифраторов (DC), мультиплексоров (MX), демультиплексоров (DMX). Приобретение навыков синтеза и анализа этих и других цифровых комбинационных устройств на их основе. Изучение работы тестовых и контрольно-измерительных приборов программы Multisim. Порядок выполнения работы. 1. Синтез шифратора размерностью 4´2 на ЛЭ. На рис.3.1 показано условное обозначение шифратора размерностью 4´2 и его таблица истинности

Рис.3.1

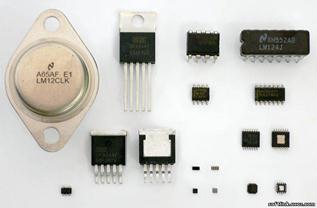

Синтезируйте схему шифратора на ЛЭ в базисе И-НЕ. Для этого используйте ЛЭ 2И-НЕ из библиотеки компонентов. Подключите входы дешифратора к источникам логических сигналов (можно использовать ключи или генератор слов), а к выходам подключите логические пробники. Протестируйте схему в соответствии с таблицей истинности данного шифратора. 2. Исследование принципа работы приоритетного шифратора размерностью 10 × 4 на основе ИС. Соберите схему, изображенную на рис.3.2. В ней используется ИС 74LS147D приоритетного шифратора с инверсными входами и выходами. Для выбора этой ИС откройте окно компонентов, выберите группу TTL, а в ней - семейство 74LS_IC. В открывшемся окне выберите ИС 74LS147D.

Рис.3.2 Для исследования работы шифратора подключите к входам ИС 9-тидвижковый переключатель (группа - basic, семейство – SWITCH, компонент - DSWPK_9), а к выходам подключите через инверторы 7-сегментный индикатор (группа Indicators, семейство HEX_DISPLAY, компонент DCD_HEX_DIG_ORANGE). Протестируйте схему и составьте таблицу истинности приоритетного шифратора. 3. Синтез дешифратора размерностью 2´4 на ЛЭ. На рис.3.3 показано условное обозначение дешифратора размерностью 2´4 и его таблица истинности.

Рис.3.3

Синтезируйте схему дешифратора 2´4 на ЛЭ в базисе И-НЕ. Подключите входы дешифратора к источникам логических сигналов, а к выходам подключите логические пробники или индикатор. Протестируйте схему в соответствии с таблицей истинности данного шифратора. 4. Исследование принципа работы дешифратора 3 × 8 на основе ИС. Соберите схему дешифратора 3 × 8 в соответствии с рис.3.4. В ней используется ИС DCD_3TO8. Для выбора этой ИС откройте окно компонентов, выберите группу Misc Digital, а в ней – семейство TIL. В открывшемся окне выберите компонент DCD_3TO8.

Рис.3.4 Протестируйте дешифратор и составьте его таблицу истинности.

5. Исследование принципа работы дешифратора семисегментного индикатора. 5.1. Соберите схему, изображенную на рис.3.5. Дешифратор семисегментного индикатора выберите из библиотеки компонентов – группа Misc Digital, семейство TIL, компонент DCD_7SEG_P. Этот дешифратор преобразует входной четырехразрядный двоично-десятичный код в десятичную цифру, отображаемую на 7-сегментном индикаторе, подключенном к выходам дешифратора.

Рис.3.5

7-сегментный индикатор, общий вид которого представлен на рис.3.6, выберите из библиотеки компонентов (группа Indicators, семейство HEX_DISPLAY, компонент SEVEN_SEG_COM_K_ORANGE).

Рис.3.6

Разверните панель генератора слов и задайте на входах A, B, C, D все комбинации двоично-десятичного кода, соответствующие десятичным числам 0 – 9. Включите схему и протестируйте дешифратор в пошаговом режиме генератора слов. При этом на 7-сегментном индикаторе должны отображаться десятичные цифры. 5.2. Подключите к выходам дешифратора вместо 7-сегментныого индикатора логические пробники. Протестируйте полученную схему и заполните таблицу функционирования дешифратора (таблица 3.1). По результатам тестирования сделайте вывод о соответствии двоичного выходного кода десятичной цифре, отображаемой на 7-сегментном индикаторе для каждой комбинации входного кода.

Таблица 3.1

6 Исследование мультиплексора размерностью 4´1 на ЛЭ. На рис.3.7 показано условное обозначение мультиплексора на 4 информационных входа D0 – D3, каждый из которых может быть подключен к единственному выходу Q с помощью задания номера входа на адресных входах А0 и А1.

Рис.3.7

Пусть работа мультиплексора 4´1 осуществляется в соответствии с ФАЛ:

Из данного выражения следует, что для синтеза мультиплексора на ЛЭ потребуется два инвертора, четыре ЛЭ типа 3И и один ЛЭ типа 4ИЛИ, т.е. всего 7 ЛЭ. 6.1 Синтез мультиплексора. Синтезируйте мультиплексор на ЛЭ в соответствии с выражением (3.1). Информационные и адресные входы схемы подключите к источникам логических сигналов посредством ключей, а на выход подключите логический пробник. Включите схему и исследуйте ее работу: подавайте с помощью ключей на информационные входы D0 – D3 логические сигналы и для каждой комбинации адресного слова определите информационный вход, подключенный к выходу. Заполните таблицу функционирования мультиплексора 4´1 (таблица 3.2). Таблица 3.2

В графе «Выход» таблицы 3.2 запишите номер информационного входа, подключенного к выходу для данной комбинации адресного слова. 6.2.. Исследование принципа работы мультиплексора 4 × 1 на основе ИС. Соберите схему, изображенную на рис.3.8. Для выбора ИС мультиплексора откройте окно компонентов, выберите группу Misc Digital, а в ней – семейство TIL. В открывшемся окне выберите компонент MUX_4TO1. Подключите к информационным входам D0 – D3 4-хполюсный движковый переключатель, а к адресным входам – ключи. Протестируйте мультиплексор, составьте его таблицу истинности и сравните ее с таблицей 3.2.

Рис. 3.8 6. Исследование принципа работы демультиплексора размерностью 1× 8 на основе ИС. Соберите схему, изображенную на рис.3.6. В ней используется ИС 74HC137D_2V–демультиплексор 1× 4 с инверсными выходами. Для выбора этой ИС откройте окно компонентов, выберите группу CMOS, а в ней - семейство 74HC_2V. В открывшемся окне выберите ИС 74HC137D_2V.

Рис.3.6 Демультиплексор 1× 8 имеет один информационный вход D, который может быть подключен к одному из восьми выходов (Y0 – Y7) с помощью задания номера выхода на адресных входах А, В, С. К его адресным входамподключите ключи или генератор слов. К входу D подключите ключ или генератор прямоугольных импульсов с частотой 1Гц. К выходам подключите логические пробники. Протестируйте демультиплексор и по результатам тестирования заполните его таблицу истинности (таблица 3.3). Таблица 3.3

7. Задания для самостоятельной работы. 7.1. Синтез ЦУ дешифратора 5х32. Синтезируйте по аналогии с предыдущим заданием схему дешифратора 5х32 на основе четырёх дешифраторов 3х8. Старшие разряды входного пятиразрядного кода e и d подключите к входам разрешения так, чтобы функции разрешения для соответствующих входов определялись следующими выражениями: e*d, e*d, e*d, e*d (для формирования последнего произведения необходим ЛЭ типа НЕ).Протестируйте схему Убедитесь в правильности его работы. 7.2. Синтез ЦУ для реализации заданной функции. 7.2.1. Синтезируйте и испытайте схемы на основе базового дешифратора и элементов 2И-НЕ или 2И, реализующие заданную функцию F. На входе разрешения установите активный уровень. Варианты задач приведены ниже. 1) F=C’*B*A’ÚC*B*AÚB’*A’; 2) F=B’*A’ÚC*B’ÚC’*B*A; 3) F=C’*AÚC*B’; 4) F=C’*A’ÚB; 5) F=C’*B’*AÚC*B’*A’ÚC’*B*A’; 6) F=C’*B’*AÚC*B’*AÚC*B’*A’; 7) F=C’*B’*A’ÚB*AÚC*B; 8) F=C*A’ÚB’*AÚC’*A. 7.2.2. Синтезируйте и испытайте схемы на основе дешифратора 3х8 и элемента И-НЕ, реализующие заданную функцию F. Один из входов разрешения используйте для подачи аргумента одного из сигналов. Варианты задач приведены ниже. 1) F=D*C’*A’ÚD*C*B*AÚD*B’*A’; 2) F=D’*B’*A’ÚD’*C*BÚD’*C’*B*A; 3) F=D*C’*AÚC*B’*A; 4) F=D’*C’*B*AÚD’*C*B*A’ÚD*C’*B*A’; 5) F=D’*C*B’*AÚD*C*B’*AÚD*C*B’*A’; 6) F=D’*C’*B’*AÚD’*B*AÚD’*C*B. 7.2.3. Разработайте, соберите и испытайте схемы на основе дешифратора, формирующие нули на указанных выходах при следующих комбинациях логических уровней на входах, заданных шестнадцатеричными числами в таблице 3.4. Таблица 3.4

7.2.4. Синтезируйте и проверьте работу схем на основе мультиплексора 8х1, реализующих заданную логическую функцию Y: 1) Y=C’*B’ÚC*A; 2) Y=B’*A’ÚC*B’ÚC’*A’; 3) Y=C’*B’*A’ÚC*B’*AÚC’*B*AÚC*B*A’; 4) Y=C*AÚB’*A’ÚC’*A’; 5) Y=D*B’*A’ÚC*BÚD’*B’*A; 6) Y=D’*B’*C’*A’ÚC*B*AÚD*C’*B; 7) Y=D*CÚB*A; 8) Y=D’*C*AÚD*B’*A’ÚC*B*A’ÚD’*C’*B; 9) Y=D*(E’*B*AÚC*B’*AÚE*C’*B); 10) Y=B’*(E*D*C*AÚE’*D’*CÚD*C’*A); 11) Y=E*(D*C*B*A’ÚC’*B’*AÚD’*B*A’); 12) Y=A’*(E’*C*B’ÚE*D*CÚD*C’*B).

Содержание отчета

1. Наименование и цель работы. 2. Перечень приборов и элементов. 3. Схемы ЦУ. 4. Результаты экспериментов. 5. Выводы в результате анализа схем ЦУ.

Контрольные вопросы

1. Понятие, назначение, классификация и условное обозначение дешифраторов, мультиплексоров, демультиплексоров. 2. Назовите логические функции, выполняемые дешифратором, мультиплексором, демультиплексором. 3. ФАЛ, таблица истинности и схема дешифратора 2×4, выполненная в базисе И-НЕ. 4. Запишите выражение, связывающее количество входов и выходов дешифратора. 5. ФАЛ, таблица истинности и схема мультиплексора 4×1, выполненная в базисе И-НЕ. 6. Принципы синтеза дешифратора 4×16 на основе нескольких дешифраторов 2×4 с управляющим входом. Сколько дешифраторов 2×4 потребуется для решения этой задачи? 7. Как построить схему демультиплексора 1×4 и схему мультиплексора 4×1 на основе дешифратора 2×4? 8. Построить схему дешифратора состояний семисегментного индикатора на ЛЭ в базисе И-НЕ для преобразования двоичных чисел в десятичные

|

F=Q=1= D0 A1 A0 + D1 A1 A0+ D2 A1 A0+ D3 A1 A0 (3.1)

F=Q=1= D0 A1 A0 + D1 A1 A0+ D2 A1 A0+ D3 A1 A0 (3.1)