Пример применения конвейеров в процессоре ОКОД.

S450

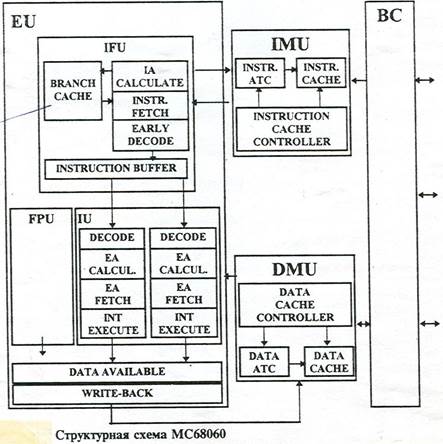

S451 Структурная схема МС68060 приведена на рис. выше.

Основными узлами МС68060 являются: · Исполнительное устройство (Execution Unit –EU); · Устройство памяти инструкций (Instruction Memory Unit –IMU); · Устройство памяти данных (Data Memory Unit –DMU); · Контроллер магистрали (BUS CONTROLLER –BC). Исполнительное устройство (EU) состоит из: · устройства выборки инструкций (Instruction Fetch Unit – IFU); · целочисленного устройства (Integer Unit -IU); · устройства с плавающей точкой (Floating Point Unit –FPU). Устройство памяти инструкций (IMU) состоит из: · кэш-памяти адресных трансляций инструкций (Instruction ATC); · кэш-памяти инструкций (Instruction Cache); · контроллера кэш-памяти инструкций (Instruction Cache Controller). Устройство памяти данных (DMU) состоит из: · кэш-памяти адресных трансляций данных (Data ATC); · кэш-памяти данных (Data Cache); · контроллера кэш-памяти данных (Data Cache Controller).

S452 Устройство выборки инструкций исполнительного устройства состоит из четырехкаскадного конвейера извлечения инструкций, кэш-памяти ветвлений и логики взаимодействия с кэш-памятью ветвлений. Конвейер извлечения инструкций обеспечивает предварительное извлечение до момента действительного использования инструкций конвейером обработки. 1-й каскад – вычисление исполнительного адреса – IA CALCULATE- обеспечивает вычисление виртуального адреса инструкции. 2-й каскад – извлечение инструкции INSTRUCTION FETCH, является главным в конвейере. 3-й каскад – предварительное декодирование EARLE DECODE. В нем происходит декодирование с целью получения информации об управлении конвейером. 4-й каскад – буфер инструкций INSTRUCTION BUFFER. Представляет собой простую буферную память, где инструкция и ее управляющая информация хранятся до момента их выборки конвейером обработки целочисленного устройства. Кэш ветвлений опрашивается на наличие достоверного входа ветвлений после генерации каждого адреса в конвейере извлечения инструкций. Если совпадение не произойдет, то конвейер продолжит последовательную выборку.

S453 Целочисленное устройство исполнительного устройства состоит из: - двух целочисленных конвейеров обработки; - логики для взаимодействия с FPU; - логики управления данными. Суперскалярное устройство двух конвейеров обеспечивает одновременное выполнение двух команд. Логика управления IU выбирает две команды из буфера инструкций IFU в каждом периоде тактовой частоты, останавливаясь только, если информация команды недостаточна, или, если существуют условия остановки конвейера обработки. Конвейеры IU структурно идентичны и именуются: первичный конвейер pOEP и вторичный конвейер sOEP. Каждый из конвейеров включает в себя 6 каскадов: 1 – каскад полного декодирования; 2 – каскад вычисления эффективного адреса операнда EA CALCULATE; 3 – каскад извлечения данных из эффективного адреса; 4 – каскад целочисленной обработки данных INT EXECUTE; 5 – каскад доступных данных результата D.A.; 6 – каскад данных обратных записей во внутрикристальный кэш данных или во внешнюю память WRITE-BACK. FPU является математическим процессором, отдельным от IU. Оно работает в стандарте ANSI IEEE 754 для арифметики с плавающей точкой и оптимизировано для получения высокой производительности при выполнении наиболее часто встречающихся команд и типов данных. (Может быть программно отключено для снижения энергопотребления). S454 IMU и DMU – два независимых устройства памяти. Каждое содержит 8-килобайтный кэш, контроллер кэша и кэш адресных трансляций (ATC). Кэш можно отключать. ATC представляет собой 64-входовые 4-путевые установочно-ассоциативные устройства, хранящие часто используемые трансляции логического адреса в физические. После получения логического адреса из IFU контроллер устройства управления памятью инициирует поиск адресной трансляции страницы в ATC. Если требуемый дескриптор не имеется в ATC, то контроллер кэша выполняет внешний цикл поиска через контроллер магистрали. После нахождения дескриптора его содержимое загружается в ATC и адрес обращения оказывается корректно оттранслированным. Контроллер магистрали ВС обеспечивает работу немультиплексированной магистрали с полным синхронным протоколом обмена, тактируемых фронтами импульсов, а также работу периферийным устройствам в асинхронном режиме и работу с периферией по мультиплексируемой во времени магистрали. Все временные характеристики могут быть сконфигурированы под требования внешней памяти.

|