Дать определение:

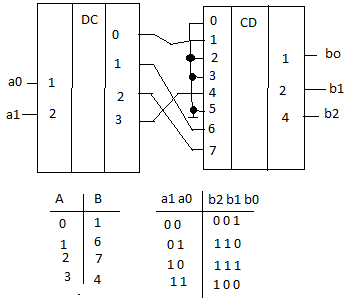

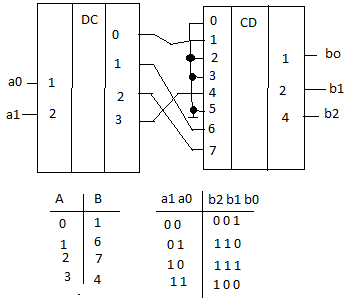

Шифратор - логическое устройство,преобразующее десятичный код в двоичный.

Компаратор - устройство,предназначенное для сравнения двух двоичных многоразрядных чисел.

Область применения схемы контроля на чётность:Cxeмa пpимeняeтcя для выявлeния oшибoк,вызвaнныx пoмexaми в линии cвязи или в блoкax пaмяти.

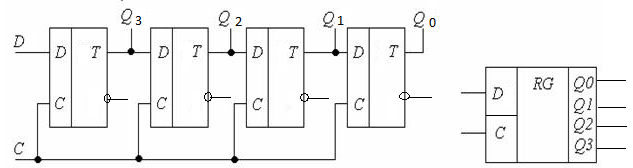

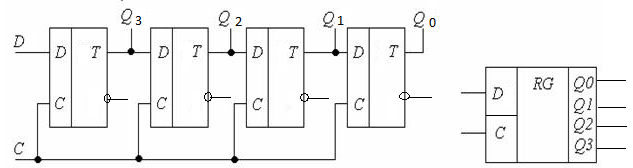

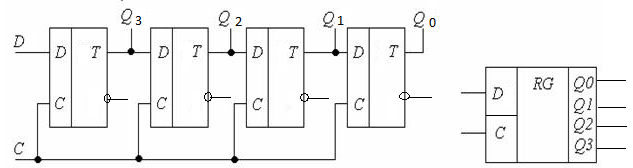

Объяснить работу: Регистр сдвига влево. Для осуществления сдвига влево необходимо в сдвиговом регистре изменить связи между триггерами,подключая выход триггера ко входу D триггера соседнего слева разряда.

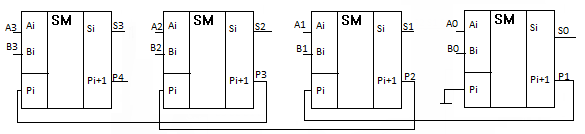

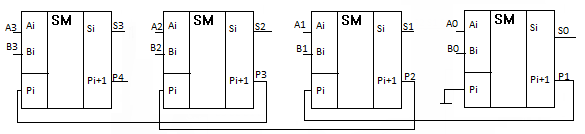

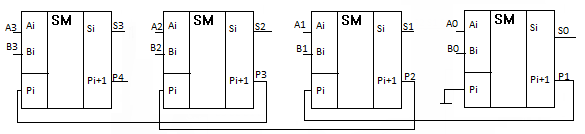

Объяснить работу: Последовательный сумматор. В сумматоре последовательного действия числа вводятся разряд за разрядом,начиная с младшего.Схема: Схема состоит из одноразрядного сумматора,выход Pi+1 которого соединён со входом Pi через D-триггер.Сдвиговые регистры служат для подачи на входы сумматора разряда в последовательной форме.С первым тактовым импульсом на входы сумматора поступают из регистров цифры улевого разряда,с D-триггера на вход Pi подаётся логический 0.Суммируя А0 и В0 формируется сумма S0 и перенос Pi принимаемый D-триггером.Второй тактовый импульс

Объяснить работу: Последовательный сумматор. В сумматоре последовательного действия числа вводятся разряд за разрядом,начиная с младшего.Схема: Схема состоит из одноразрядного сумматора,выход Pi+1 которого соединён со входом Pi через D-триггер.Сдвиговые регистры служат для подачи на входы сумматора разряда в последовательной форме.С первым тактовым импульсом на входы сумматора поступают из регистров цифры улевого разряда,с D-триггера на вход Pi подаётся логический 0.Суммируя А0 и В0 формируется сумма S0 и перенос Pi принимаемый D-триггером.Второй тактовый импульс  осуществляет в регистрах сдвиг на один разряд вправо и суммируются следующие разряды. Достоинтсва: малые аппаратные затраты.Недостаток: низкое быстродействие.

осуществляет в регистрах сдвиг на один разряд вправо и суммируются следующие разряды. Достоинтсва: малые аппаратные затраты.Недостаток: низкое быстродействие.

Построить схему: Схема параллельного сумматора.

Сумматор параллельного действия с последовательной передачей переноса:

При передаче слагаемых,цифры разрядов поступают на соответствущие одноразрядные сумматоры.Каждый из сумматоров формирует свой разряд суммы и перенос, передаваемый на вход следующего, более старшего сумматора.Схема имеет среднее быстродействие.

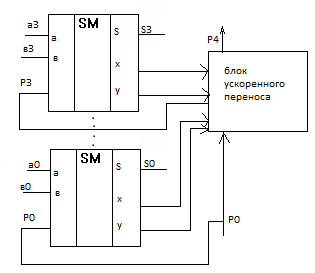

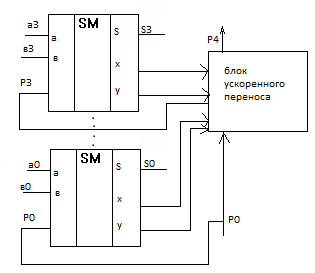

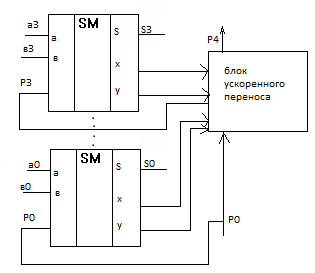

Сумматор параллельного действия с параллельной передачей переноса:

Блок ускоренного переноса производит формирование переносов в параллельной форме.Переносы из этого блока поступают во все сумматоры одновременно. При этом сумматоры не содержат цепей формирования переносов, они формируют сумму Si и величины xi,yi, которые необходимы для формирования переносов.Возможны следующие ситуации: 1)yi=1 - означает, что в итом разряде перенос Pi+1 в следующий разряд, необходимо формировать независимо от поступления в данный разряд переноса из предыдущего разряда. 2)xi=1 - означает,что в итом разряде перенос Pi+1 должен формироваться только при условии поступления переноса Pi из предыдущего разряда:р1=y0+x0*p0 и т.д.

Блок ускоренного переноса производит формирование переносов в параллельной форме.Переносы из этого блока поступают во все сумматоры одновременно. При этом сумматоры не содержат цепей формирования переносов, они формируют сумму Si и величины xi,yi, которые необходимы для формирования переносов.Возможны следующие ситуации: 1)yi=1 - означает, что в итом разряде перенос Pi+1 в следующий разряд, необходимо формировать независимо от поступления в данный разряд переноса из предыдущего разряда. 2)xi=1 - означает,что в итом разряде перенос Pi+1 должен формироваться только при условии поступления переноса Pi из предыдущего разряда:р1=y0+x0*p0 и т.д.

Дать определение:

Шифратор - логическое устройство,преобразующее десятичный код в двоичный.

Компаратор - устройство,предназначенное для сравнения двух двоичных многоразрядных чисел.

Область применения схемы контроля на чётность:Cxeмa пpимeняeтcя для выявлeния oшибoк,вызвaнныx пoмexaми в линии cвязи или в блoкax пaмяти.

Объяснить работу: Регистр сдвига влево. Для осуществления сдвига влево необходимо в сдвиговом регистре изменить связи между триггерами,подключая выход триггера ко входу D триггера соседнего слева разряда.

Объяснить работу: Последовательный сумматор. В сумматоре последовательного действия числа вводятся разряд за разрядом,начиная с младшего.Схема: Схема состоит из одноразрядного сумматора,выход Pi+1 которого соединён со входом Pi через D-триггер.Сдвиговые регистры служат для подачи на входы сумматора разряда в последовательной форме.С первым тактовым импульсом на входы сумматора поступают из регистров цифры улевого разряда,с D-триггера на вход Pi подаётся логический 0.Суммируя А0 и В0 формируется сумма S0 и перенос Pi принимаемый D-триггером.Второй тактовый импульс

Объяснить работу: Последовательный сумматор. В сумматоре последовательного действия числа вводятся разряд за разрядом,начиная с младшего.Схема: Схема состоит из одноразрядного сумматора,выход Pi+1 которого соединён со входом Pi через D-триггер.Сдвиговые регистры служат для подачи на входы сумматора разряда в последовательной форме.С первым тактовым импульсом на входы сумматора поступают из регистров цифры улевого разряда,с D-триггера на вход Pi подаётся логический 0.Суммируя А0 и В0 формируется сумма S0 и перенос Pi принимаемый D-триггером.Второй тактовый импульс  осуществляет в регистрах сдвиг на один разряд вправо и суммируются следующие разряды. Достоинтсва: малые аппаратные затраты.Недостаток: низкое быстродействие.

осуществляет в регистрах сдвиг на один разряд вправо и суммируются следующие разряды. Достоинтсва: малые аппаратные затраты.Недостаток: низкое быстродействие.

Построить схему: Схема параллельного сумматора.

Сумматор параллельного действия с последовательной передачей переноса:

При передаче слагаемых,цифры разрядов поступают на соответствущие одноразрядные сумматоры.Каждый из сумматоров формирует свой разряд суммы и перенос, передаваемый на вход следующего, более старшего сумматора.Схема имеет среднее быстродействие.

Сумматор параллельного действия с параллельной передачей переноса:

Блок ускоренного переноса производит формирование переносов в параллельной форме.Переносы из этого блока поступают во все сумматоры одновременно. При этом сумматоры не содержат цепей формирования переносов, они формируют сумму Si и величины xi,yi, которые необходимы для формирования переносов.Возможны следующие ситуации: 1)yi=1 - означает, что в итом разряде перенос Pi+1 в следующий разряд, необходимо формировать независимо от поступления в данный разряд переноса из предыдущего разряда. 2)xi=1 - означает,что в итом разряде перенос Pi+1 должен формироваться только при условии поступления переноса Pi из предыдущего разряда:р1=y0+x0*p0 и т.д.

Блок ускоренного переноса производит формирование переносов в параллельной форме.Переносы из этого блока поступают во все сумматоры одновременно. При этом сумматоры не содержат цепей формирования переносов, они формируют сумму Si и величины xi,yi, которые необходимы для формирования переносов.Возможны следующие ситуации: 1)yi=1 - означает, что в итом разряде перенос Pi+1 в следующий разряд, необходимо формировать независимо от поступления в данный разряд переноса из предыдущего разряда. 2)xi=1 - означает,что в итом разряде перенос Pi+1 должен формироваться только при условии поступления переноса Pi из предыдущего разряда:р1=y0+x0*p0 и т.д.

Объяснить работу: Последовательный сумматор. В сумматоре последовательного действия числа вводятся разряд за разрядом,начиная с младшего.Схема: Схема состоит из одноразрядного сумматора,выход Pi+1 которого соединён со входом Pi через D-триггер.Сдвиговые регистры служат для подачи на входы сумматора разряда в последовательной форме.С первым тактовым импульсом на входы сумматора поступают из регистров цифры улевого разряда,с D-триггера на вход Pi подаётся логический 0.Суммируя А0 и В0 формируется сумма S0 и перенос Pi принимаемый D-триггером.Второй тактовый импульс

Объяснить работу: Последовательный сумматор. В сумматоре последовательного действия числа вводятся разряд за разрядом,начиная с младшего.Схема: Схема состоит из одноразрядного сумматора,выход Pi+1 которого соединён со входом Pi через D-триггер.Сдвиговые регистры служат для подачи на входы сумматора разряда в последовательной форме.С первым тактовым импульсом на входы сумматора поступают из регистров цифры улевого разряда,с D-триггера на вход Pi подаётся логический 0.Суммируя А0 и В0 формируется сумма S0 и перенос Pi принимаемый D-триггером.Второй тактовый импульс  осуществляет в регистрах сдвиг на один разряд вправо и суммируются следующие разряды. Достоинтсва: малые аппаратные затраты.Недостаток: низкое быстродействие.

осуществляет в регистрах сдвиг на один разряд вправо и суммируются следующие разряды. Достоинтсва: малые аппаратные затраты.Недостаток: низкое быстродействие.

Блок ускоренного переноса производит формирование переносов в параллельной форме.Переносы из этого блока поступают во все сумматоры одновременно. При этом сумматоры не содержат цепей формирования переносов, они формируют сумму Si и величины xi,yi, которые необходимы для формирования переносов.Возможны следующие ситуации: 1)yi=1 - означает, что в итом разряде перенос Pi+1 в следующий разряд, необходимо формировать независимо от поступления в данный разряд переноса из предыдущего разряда. 2)xi=1 - означает,что в итом разряде перенос Pi+1 должен формироваться только при условии поступления переноса Pi из предыдущего разряда:р1=y0+x0*p0 и т.д.

Блок ускоренного переноса производит формирование переносов в параллельной форме.Переносы из этого блока поступают во все сумматоры одновременно. При этом сумматоры не содержат цепей формирования переносов, они формируют сумму Si и величины xi,yi, которые необходимы для формирования переносов.Возможны следующие ситуации: 1)yi=1 - означает, что в итом разряде перенос Pi+1 в следующий разряд, необходимо формировать независимо от поступления в данный разряд переноса из предыдущего разряда. 2)xi=1 - означает,что в итом разряде перенос Pi+1 должен формироваться только при условии поступления переноса Pi из предыдущего разряда:р1=y0+x0*p0 и т.д.