PCI Express — ключевые отличия от PCI

Подробнее остановимся на ключевых отличиях PCI Express от PCI:

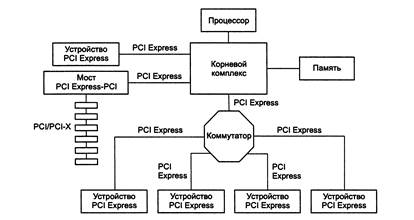

Элементы и топология соединений PCI Express Соединение PCI Express (PCI Express Link) — это пара встречных симплексных каналов, соединяющих два компонента. По этим каналам передаются пакеты, несущие команды и данные транзакций, сообщения и управляющие посылки. Канал может быть образован одной или несколькими линиями передачи сигналов (Lane); применение нескольких линий позволяет масштабировать пропускную способность канала. В PCI Express с помощью пакетного протокола реализуются все транзакции чтения и записи, используемые в PCI, причем в расщепленном варианте (как в PCI-X). Таким образом, здесь фигурируют запросчик (requester) и исполнитель (completer) транзакции. В PCI Express рассматриваются четыре пространства: 1) пространство памяти (выделяется при конфигурировании), 2) пространство ввода-вывода (выделяется при конфигурировании), 3) конфигурационное пространство (конфигурационные регистры адресуются по идентификатору – номеру шины, устройства) и 4) пространство сообщений - используется для передачи в виде пакетов «внеполосных» сигналов PCI: прерываний по линиям INTx, сигналов управления и т. п. Порт PCI Express содержит передатчик, приемник и узлы, необходимые для сборки-разборки пакетов. Пример топологии шины PCI-Express приведен на рис. 5.26.

Рис. 5.26 Топология «фабрики» PCI Express

Центральным элементом архитектуры является корневой комплекс (root complex), соединяющий иерархию ввода-вывода с центром — процессором (одним или несколькими) и памятью. Корневой комплекс может иметь один и более портов PCI Express, каждый из этих портов определяет свой домен иерархии (hierarchy domain). Каждый домен состоит из одной конечной точки (endpoint) или субиерархии — нескольких конечных точек, связанных коммутаторами. Наличие непосредственных одноранговых коммуникаций между элементами разных доменов обязательным не является, но может иметь место в конкретных реализациях. Для обеспечения прозрачных одноранговых коммуникаций в корневом комплексе должны присутствовать коммутаторы. Возможность взаимодействия центрального процессора с любым устройством любого домена безусловна, как и возможность обращения любого устройства к памяти. Корневой комплекс должен генерировать запросы к конфигурационному пространству — его роль аналогична главному мосту PCI. Конечная точка — это устройство, способное инициировать или/и исполнять транзакции PCI Express от своего имени или от имени устройства, не являющегося устройством PCI Express (например, от имени хост-контролера USB). Конечная точка должна быть видима в одном из доменов иерархии — представлять в нем свои конфигурационные регистры и отвечать как исполнитель на конфигурационные запросы. В качестве механизма сигнализации прерываний все конечные точки используют MSI. В PCI Express рассматриваются два типа конечных точек: «наследники» (legacy) и новые точки, построенные по идеологии PCI Express. К «наследным» точкам имеется ряд послаблений в плане адресации памяти, перемещаемости ресурсов (из пространства ввода-вывода в пространство памяти) и некоторых нюансов. Коммутатор (switch) имеет несколько портов PCI Express. Логически он представляет собой несколько виртуальных мостов PCI-PCI, соединяющих порты коммутатора со своей внутренней локальной шиной. Однако тех издержек, которые вносят «настоящие» мосты PCI, коммутатор не вносит. Коммутатор транслирует между портами пакеты всех типов, основываясь на адресной информации, актуальной для пакета данного типа. Арбитраж между портами коммутатора может учитывать виртуальные каналы и, соответственно, взвешенно распределять пропускную способность. Коммутатор не имеет права разбивать пакеты на более мелкие (у мостов PCI такое право имеется). Мост PCI-Express-PCI соединяет иерархию шин PCI/PCI-X с «фабрикой» ввода-вывода. Конфигурирование «фабрики» осуществляется либо со 100-процентной совместимостью с конфигурационным механизмом PCI 2.3, либо с использованием расширенного конфигурационного пространства PCI-X. Каждое соединение PCI Express с помощью виртуальных мостов отображается в виде логической шины PCI со своим номером. Логически устройства отображаются в конфигурационном пространстве как устройства PCI, каждое из которых может иметь 1-8 функций со своим набором конфигурационных регистров. Архитектурная модель PCI Express.

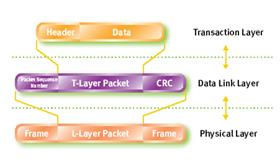

Уровень транзакций (transaction layer) — верхний уровень архитектуры, отвечающий за сборку и разборку пакетов TLP (Transaction Layer Packet — пакет уровня транзакций). Эти пакеты используются для транзакций чтения и записи, а также для сообщений о событиях некоторых типов. Каждый пакет TLP имеет уникальный идентификатор, который позволяет направить ответный пакет его отправителю. Уровень транзакций отвечает и за управление потоком. Канальный уровень (data link layer), промежуточный в стеке, отвечает за управление связью, обнаружение ошибок и организацию повторных передач вплоть до успеха или признания отказа соединения. К пакетам, полученным от уровня транзакций, канальный уровень добавляет свои заголовки (номера пакетов и контрольные коды). Канальный уровень и сам является генератором и получателем пакетов DLLP (Data Link Layer Packet — пакет канального уровня), используемых для управления соединением. Физический уровень (physical layer) изолирует канальный от всех подробностей передачи сигналов. Он состоит из двух субблоков. Логический субблок при передаче выполняет распределение данных по линиям, скремблирование, кодирование по схеме 8В/10В1, кадрирование и преобразование в последовательный код. При приеме выполняются обратные действия. Символы, добавляемые при кодировании 8В/10В, используются для служебной сигнализации. Логический субблок отвечает и за согласование соединения, инициализацию и т. п. Электрический субблок отвечает за электрическое согласование, синхронизацию, обнаружение приемника. Уровневая модель, принятая в PCI Express, позволяет, не затрагивая остальных уровней, сменить физический уровень или его субблоки, когда появятся более эффективные схемы кодирования и сигнализации. Интерфейс между физическим и канальным уровнями зависит от реализации этих компонентов и выбирается их разработчиком. Интерфейс физического уровня четко специфицирован, что обеспечивает возможность соединения устройств разного происхождения. Для тестирования на соответствие электрическим параметрам достаточно подключить устройство PCI Express к специальному тестеру. Надежность передачи и целостность данных

Уровень транзакций формирует пакетыTLP, в которых содержатся код команды, адресная информация, данные и некоторые другие поля. Для обеспечения надежной доставки пакетов TLP канальный уровень при передаче снабжает их своим заголовком, содержащим 12-битный последовательный номер TLP, и 32-битным полем LCRC (CRC канального уровня). Таким образом, канальный уровень к каждому пакету TLP добавляет 6 байт накладных расходов. На каждый пакет TLP передатчик должен получить положительное подтверждение Ack— пакет канального уровня (DLLP). Если подтверждение не приходит, то механизм тайм-аута заставляет передатчик повторить посылку пакета. Предусмотрен и пакет отрицательного подтверждения Nak,вызывающий повторную передачу без ожидания. Физический уровень вводит свое обрамление передаваемых пакетов: перед началом пакета передается специальный символ STP (для TLP-пакета) или SD (для DLLP-пакета); после пакета — символ END. Эти специальные символы отличаются от символов, представляющих данные после кодирования 8В/10В.

Для обеспечения надежности транзакций и целостности данных применяется CRC-контроль всех транзакций и управляющих пакетов. Запросчик считает транзакцию выполненной по получении подтверждающего сообщения от исполнителя (подтверждение отсутствует только для записей, отправленных в основную память). Обработка ошибок в минимальном варианте аналогична PCI, причем обнаруженные ошибки отображаются в конфигурационных регистрах функций (в регистре состояния). Расширенные возможности сообщений об ошибках дают исходную информацию для развитых процедур изоляции отказов и восстановления, а также мониторинга и регистрации (logging) ошибок. Ошибки делятся на три группы, что позволяет использовать адекватные процедуры восстановления: · исправимые (correctable) ошибки автоматически вызывают аппаратную процедуру восстановления (повтора) и не требуют программного вмешательства для нормального исполнения транзакции; · неисправимые фатальные (fatal) ошибки для надежного возобновления работы требуют сброса, в результате которого могут пострадать транзакции, не имеющие прямого отношения к ошибке; · неисправимые нефатальные (non-fatal) ошибки не требуют сброса для возобновления работы — в результате этих ошибок могут быть потеряны лишь несколько транзакций, затронутых ошибкой.

|