Триггеры

Основные сведения. Триггерами называют большой класс электронных устройств, обладающих способностью длительно находиться в одном из двух или болееустойчивых состояний и чередовать их под воздействием внешних сигналов. В отличие от комбинационных логических схем, триггеры - это логические устройства с памятью. Их выходные сигналы в общем случае зависят не только от сигналов, приложенных к входам в данный момент времени, но и от сигналов, воздействовавших на них ранее. В зависимости от свойств, числа и назначения входовтриггеры можно разделить на несколько видов. Информационные сигналы поступают на входы А и В логического устройства (ЛУ) и преобразуются в сигналы, поступающие на внутренние входы S' и R' ячейки памяти (ЯП). Процесс преобразования информационных сигналов осуществляется при воздействии сигналов, подаваемых на вход Т предустановки и вход С синхронизации. Вход Т обычно используется для разрешения приема информации, а исполнительный вход С обеспечивает тактируемый прием информации. В простейшем триггере ЛУ может отсутствовать, а информационные сигналы подаются непосредственно на входы S и R ЯП.

Виды триггеров. Триггер Т (рис. 8.1) можно представить в общем случае как устройство, состоящее из ячейки памяти ЯП и логического устройства ЛУ управления, преобразующего входную информацию в комбинацию сигналов, под воздействием которых ЯП принимает одно из двух устойчивых состояний. При наличии входа С триггер называют синхронным, а при его отсутствии асинхронным. Изменение состояния асинхронного триггера происходит сразу же после соответствующего изменения потенциалов на его информационных входах А и В. В синхронном триггере изменение состояния может произойти только в момент присутствия соответствующего сигнала на входе С. Синхронизация может осуществляться импульсом (потенциалом) или фронтом (перепадом потенциала). В первом случае сигналы на информационных входах оказывают влияние на состояние триггера только при разрешающем потенциале на входе С. Во втором случае воздействие информационных сигналов проявляется только в момент изменения потенциала на входе С, т. е. при переходе его от 1 к 0 или от 0 к 1. Универсальные триггеры могут работать как в синхронном, так и в асинхронном режимах. Основные типы триггеров в интегральном исполнении получили следующие названия: SR-триггер, JK-триггер, D-триггер, T-триггер. SR-триггер имеет два информационных входа S и R. Подача на вход S сигнала 1, а на вход R сигнала 0 устанавливает на выходе Q триггера сигнал 1. Наоборот, при сигналах S=0 и R= 1 сигнал на выходе триггера Q=0. Функционирование SR-триггера определяется уравнениями: Qn=(S+ Для SR-триггера комбинация S=1 и R= 1 является запрещенной. После такой комбинации информационных сигналов состояние триггера будет неопределенным: на его выходе Q может быть 0 или 1. Существуют разновидности SR-триггеров, называемые Е-, R- и S-триггерами, для которых сочетание S=R=1 не является запрещенным. Е-триггер при S=R=1 не изменяет своего состояния (Qn=Qn-1). S-триггер при S=R= l устанавливается в состояние Q=1, а R-триггер в этом случае устанавливается в состояние Q=0.

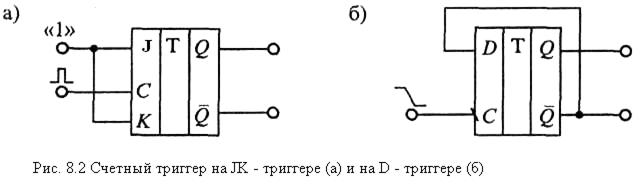

SR-триггеры могут быть асинхронными или синхронными (в этом случае у них имеется вход С). JK-триггер имеет также два информационных входа J и К. Подобно SR-триггеру, в JK-триггере J и К – это входы установки выхода Q триггера в состояние 1 или 0. Однако, в отличие от SR-триггера, в JK-триггере наличие J=K=1 приводит к переходу выхода Q триггера в противоположное состояние при поступлении синхронизирующего импульса. JK-триггеры синхронизируются только перепадом потенциала на входе С. Условие функционирования JK-триггера имеет вид: Qn=(JQ+KQ)n-1 D-триггер, или триггер задержки, при поступлении синхросигнала на вход С устанавливается в состояние, соответствующее потенциалу на входе D. Уравнение функционирования D-триггера имеет вид: Qn=Dn-A. Это уравнение показывает, что выходной сигнал Qn изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, т. е. с задержкой на один период импульсов синхронизации (Delay - задержка). Синхронизация D-триггера может осуществляться импульсом или фронтом., T - триггер, или счетный триггер, изменяет состояние выхода по фронту импульса на входе C. Кроме синхровхода С T-триггер может иметь подготовительный вход Т. Сигнал на этом входе разрешает (при T=1) или запрещает (при T=0) срабатывание триггера от фронтов импульсов на входе С. Функционирование T-триггера определяется уравнением: Qn=(QT+QT)n -1 Из этого уравнения следует, что при T=1 соответствующий фронт сигнала на входе C переводит триггер в противоположное состояние. Счетный T-триггер можно построить на JK - триггере или на D-триггере. Для построения T-триггера на JK-триггере нужно сделать входы J=K=1 (рис. 8.2 а). Тогда каждый импульс на входе С будет изменять состояние триггера на противоположное, т. е. он превратится в T-триггер. Для построения счетного T-триггера на D-триггере необходимо соединить его вход D с инверсным выходом Интегральные микросхемы триггеров. Промышленность выпускает большое количество интегральных микросхем триггеров, построенных на диодно-транзисторной логике (ДТЛ), транзисторно-транзисторной логике (ТТЛ), эмиттерно-связанной логике (ЭСЛ), комплиментарных полевых транзисторах (КМОП). В табл. 8.1 приведены основные типы триггеров различных серий интегральных микросхем. Условное обозначение интегральных микросхем триггеров состоит из обозначения серии (трех или четырех цифр), функционального назначения (двух букв) и порядкового номера разработки (от одной до трех цифр).

По функциональному назначению триггеры имеют следующие обозначения: ТР - SR-триггеры, ТВ - JK-триггеры, ТМ — D-триггеры, ТТ — T-триггеры, ТП — прочие триггеры. Интегральный триггер 155ТB1 имеет дополнительные внешние Таблица 8.1 Параметры интегральных микросхем триггеров

работает как JK-триггер. Кроме того, входы J и К имеют входную логику типа И. Состояния триггера 155ТВ1 приведены в табл. 8.3. Интегральный D-триггер 555ТМ2 также имеет дополнительные

Таблица 8.2 Состояния триггера 555ТР2

Примечание: х - безразличное состояние (т. е. 0 или 1).

Таблица 8.3 Состояния триггера 155ТВ1.

Таблица 8.4. Состояния триггера 555ТМ2

8.2 Счетчики импульсов

Основные определения и виды счетчиков. Счетчиком называют цифровое устройство, предназначенное для подсчета числа импульсов. В процессе работы счетчик последовательно изменяет свое состояние в определенном порядке. Длина списка разрешенных состояний счетчика называется модулем счета Кс. Одно из возможных состояний счетчика принимается за начальное. Если счетчик начал счет от начального состояния, то каждый импульс, кратный модулю счета Kc снова устанавливает счетчик в начальное состояние, а на выходе счетчика появляется сигнал переноса Р (или займа Z). Последовательность внутренних состояний счетчика можно кодировать различными способами. Чаще всего используют двоичное (двоичные счетчики) или двоично-десятичное (декадные счетчики) кодирование. Если коды расположены в возрастающем порядке, то счетчик называют суммирующим (Up-counter). Счетчики, у которых коды расположены в убывающем порядке, называют вычитающими (Down-counter), а счетчики, у которых направление перебора кода может изменяться, называют реверсивными (Up/Down counter).

Если для работы счетчика требуется наличие синхросигнала, то такой счетчик называют синхронным. Счетчики, которые работают без синхросигналов, называют асинхронными. Счетчики могут быть с предварительной установкой и без нее. Для предварительной установки начального состояния счетчика используются специальные входы предустановки. Установка начального состояния счетчика производится только по специальной команде записи. Во время работы счетчика в счетном режиме входы предустановки блокируются и на работу счетчика не влияют. Счетчики с предварительной установкой называют также программируемыми, так как они позволяют изменять модуль счета К с,который можно рассчитать по формуле

Kc=Sn2n+Sn-12n-1+…+S222+S121+S020, (8.1)

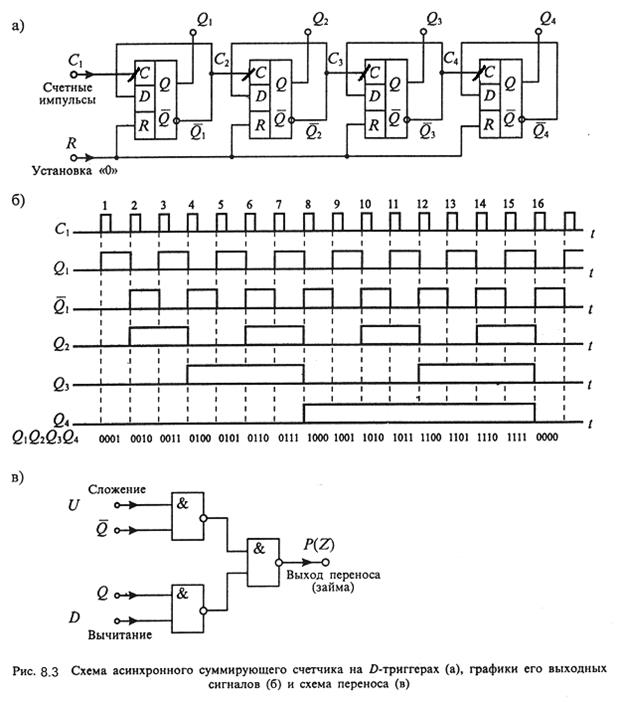

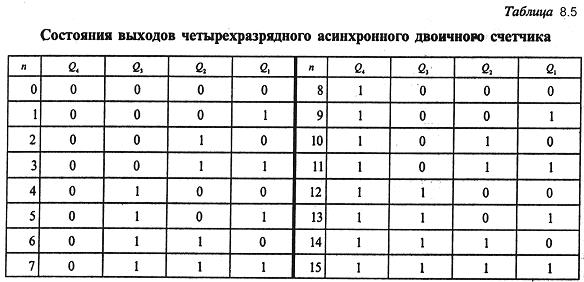

где Sk= 0 или 1. Асинхронные счетчики. Асинхронный суммирующий счетчик можно выполнить на счетных триггерах. Простейший четырехразрядный счетчик на Д- триггерах, работающий в счетном режиме, показан на рисунке 8.3 а). При поступлении счетных импульсов на вход С1 триггеры счетчика будут изменять свои состояния, описываемые последовательно возрастающими двоичными числами. В табл. 8.5 приведена последовательность состояния выходов триггеров такого счетчика.Для приведения счетчика в начальное состояние используется сигнал сброса R, поступающий одновременно на все входы Д- триггеров. При построении асинхронного вычитающего счетчика достаточно заменить прямые выходы Q на инверсные. В этом случае при поступлении импульса сброса R на всех выходах счетчика установятся единичные уровни, а при поступлении счетных импульсов на вход С1 триггеры счетчика будут изменять свои состояния, описываемые последовательно убывающими двоичными числами. Для построения асинхронного реверсивного счетчика, который может работать как в режиме суммирования, так и в режиме вычитания, необходимо с помощью логической схемы обеспечить подачу сигналов с инверсного выхода Q\ (при суммировании) или с прямого выхода Q (при вычитании) от предыдущего триггера на счетный вход последующего, как показано на рис. 8.3в. Эта схема включается между выходом одного разряда счетчика и входом другого и, в зависимости от управляющих сигналов — сложение (U) или вычитание В асинхронном счетчике с приходом каждого последующего импульса на вход С1 переключаются сразу несколько триггеров. Однако переключение этих триггеров происходит не одновременно, а с некоторой задержкой относительно друг друга. Это приводит к задержке в установлении выходного кода после поступления счетного импульса на вход C1. При большом числе разрядов счетчика задержка выходного сигнала может быть значительной и сравнимой с периодом поступления счетных импульсов на вход С1. Как видно из временных диаграмм, приведенных на рис. 8,3 б, триггеры в асинхронном последовательном счетчике работают с различной частотой переключения. Максимальную частоту имеет первый триггер, а частоты переключения

каждого последующего триггера вдвое меньше. Поэтому в качестве первого триггера нужно использовать самый быстродействующий триггер, а быстродействие других триггеров может быть ниже. Для повышения быстродействия можно также использовать ускоренное формирование сигнала переноса между разрядами счетчика.

Другой вариант счетчика (рис. 8.4) характеризуется наибольшим быстродействием, так как в нем реализована схема параллельного переноса. Смена состояний счетчика та же, что и у предыдущего, но время, необходимое на установление нового состояния, значительно меньше, поскольку счетные импульсы воздействуют одновременно на все триггеры. Условие переключения определяет логический элемент И, который на входе V данного разряда формирует разрешающий переключение сигнал, если предыдущие разряды имеют состояние 1. Таким образом, с поступлением каждого счетного импульса переключаются те триггеры, которым предшествуют разряды с состоянием 1 на выходах.

Пример реверсивного счетчика приведен на рис.8.5,а. В его схеме предусмотрены два входа для счетных импульсов, обозначенные С+ и С_. В режиме сложения импульсы должны поступать на вход С+, в режиме вычитания — на вход С_, причем на незадействованном входе должно быть напряжение высокого уровня. Для обеспечения работы счетчика необходимо устройство коммутации импульсов на соответствующий вход. Один из вариантов (рис.8.5,б) включает RS-триггер и два логических элемента И-НЕ. При сигнале V+ = l, V_=0 на прямом выходе триггера устанавливается напряжение высокого уровня, элемент D1 открывается и коммутирует счетные импульсы на вход С+. При сигнале управления V_ = l, V+=0 счетные импульсы поступают на вход С_, и счетчик работает в режиме вычитания.

Счетчик на рис.8.5, а имеет два выхода для сигналов переноса: выход «≥15» для сигнала прямого переноса, используемого при работе счетчика в режиме суммирования, и выход «≤0» для сигнала обратного переноса, используемого при работе счетчика в режиме вычитания. Оба выхода переноса используют при наращивании разрядности счетчика так, как это показано на рис. 8,5, б для двух ИС К155ИЕ7. Подключение второй ИС расширяет диапазон счетного устройства до 256 импульсов. Дальнейшее наращивание разрядности счетчика производится аналогичным соединением ИС.

Двоичные четырехразрядные счетчики достаточно полно представлены в сериях ИС (табл.8.6). Как правило, ИС двоичного счетчика содержит четыре разряда, может иметь выходы сигналов переноса и, следовательно, допускает непосредственное соединение с другой такой же ИС при наращивании разрядности счетчика. Во многих ИС счетчиков предусмотрены дополнительные входы предварительной установки состояния (входы предустановки), какие имеют, например, ИС на рис.8.5. Входы предустановки используют при реализации делителей. Наряду с двоичными широкое распространение получили двоично-десятичные счетчики. В отличие от двоичных они имеют число состояний, равное 10, а не 2n. В таком счетчике четыре триггера, но шесть «лишних» состояний исключены.

Счетчик в режиме суммирования проходит состояния в соответствии с табл.8.5 до позиции с номером 9, после которой он обнуляется. Примеры ИС четырехразрядных двоично-десятичных счетчиков приведены в табл.8.7. Наглядное представление о системе управляющих сигналов позволяет получить ИС четырехразрядного реверсивного двоично-десятичного счетчика К561ИЕ14 (рис.8.5, в). Вход C является счетным. Сигнал на входе «±1» управляет направлением счета: при напряжении высокого уровня осуществляется суммирование, при напряжении низкого уровня — вычитание. Вход Ро предназначен для сигнала разрешения (при напряжении низкого уровня) или запрещения (при напряжении высокого уровня) счета. Входы предустановки Dl— D4 предназначены для записи в счетчик поданного на них кода при наличии разрешающего сигнала V=l. Результат счета снимается с выходов Q1 — Q4, сигнал переноса при заполнении счетчика единицами—с инверсного выхода Р.

* Реверсивные **Сдвоенный четырехразрядный. ***Счетчик 14-разрядный. ****Значения параметров при 5 В.

* Реверсивные **Значения параметров при 5 В

|

Q)n-1; SR = 0.

Q)n-1; SR = 0. , т. е. сделать D=

, т. е. сделать D=

и

и

, на вход последующего разряда поступает сигнал переноса Р или сигнал займа Z.

, на вход последующего разряда поступает сигнал переноса Р или сигнал займа Z.

Двоичные счетчикиТаблица 8.6

Двоичные счетчикиТаблица 8.6