Аналогично функционирует приоритетный шифратор К555ИВ2, отличительной особенностью которого является наличие выходов с тремя состояниями, что

Рис. 15.4. Условное схематичное изображение шифратора К555ИВ1 (а) и расширенный шифратор форматом 16х4 (б) облегчает каскадирование шифраторов. Другой приоритетный шифратор К555ИВЗ имеет формат 10х4 и функционирует аналогично предыдущему. Дешифратором называют преобразователь двоичного я-разрядного кода в унитарный 2"-разрядный код, все разряды которого, за исключением одного, равны нулю. Дешифраторы бывают полные и неполные. Для полного дешифратора выполняется условие:

где п — число входов, а N — число выходов. В неполных дешифраторах имеется п входов, но реализуется N<2"; выходов. Так, например, дешифратор, имеющий 4 входа и 10 выходов будет неполным, а дешифратор, имеющий 2 входа и 4 выхода, будет полным. Рассмотрим принцип построении дешифратора на примере преобразования трехразрядного двоичного кода в унитарный код. Если считать, что входы и выходы упорядочены по возрастающим номерам, т. е. считать, что коду 000 соответствует выход Ко, коду 001 — выход у) и т. д., то для полного дешифратора можно записать восемь упорядоченных уравнений:

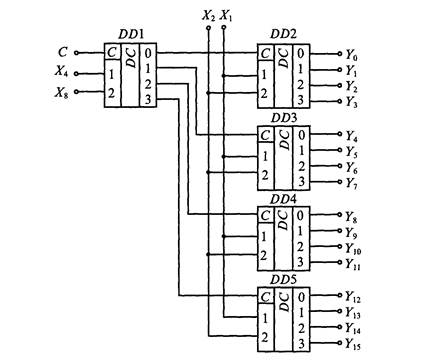

Реализовать восемь уравнений (15.3) можно с помощью восьми трехвходовых элементов И. Полученная схема дешифратора приведена на рис. 15.5 а, а его условное схематичное изображение приведено на рис. 15.5 б. Для расширения числа входов и выходов используют каскадное включение дешифраторов. На рис. 15.6 показана группа из пяти дешифраторов, соединенних последовательно в два каскада. Все дешифраторы одинаковые. Кроме кодовых входов каждый дешифратор имеет вход стробирующего сигнала (вход С). Сигнал на выходе дешифратора появляется только при С=1. Если С=0, то на всех выходах дешифратора будут нули, т. е. дешифратор заперт. На входы первого дешифратора DD\ подаются старшие разряды Хц и Xs. числа, которое нужно дешифрировать. Таким образом, дешифратор DDI определяет, какой из четырех дешифраторов DD2... DD5 из подключенных к нему будет выполнять дешифрирование младших разрядов числа. Выходные сигналы первого дешифратора подключены к стробирующим входам С остальных и разрешают их работу. Младшие разряды дешифрируемого числа X, и Х-г подаются на входы дешифраторов DD2... DD5. Однако выполнять дешифрирование этих разрядов будет только тот дешифратор, который включен сигналом, поданным на вход С от дешифратора старших разрядов. Рис. 15.5. Схема дешифратора 3х8 (а) и его условное схематичное изображение (б) Так, например, при дешифрировании числа 1001 на вход поступает код 10, которым возбуждается выход 2. В этом случае включается дешифратор DD4, на вход которого подан код 01 младших разрядов дешифрируемого числа. В результате будет возбужден выход 1 дешифратора Z)D4, при этом на выходе появится сигнал У9, что соответствует выбранному входному коду. Для расширения числа входов и выходов дешифраторов можно также воспользоваться параллельным или прямоугольным дешифратором, схема которого приведена на рис. 15.7. Схема прямоугольного дешифратора состоит из двух ступеней. Первая ступень состоит из двух дешифраторов DD\ и DD2, первый из которых дешифрует младшие разряды Х\ и Х^ входного числа, а второй — старшие разряды Х^ и Х^ Вторая ступень состоит из N элементов 2И-НЕ. Все элементы 2И-НЕ разделены на строки и столбцы: строками управляет дешифратор первой ступени на DD\, а столбцами управляет дешифратор DD2, Схема, приведенная на рис. 15.7, соответствует полному дешифратору. Если исключить некоторые из элементов 2И-НЕ, то получим неполный дешифратор с уменьшенным числом выходов. Рис 156 Каскадное включение дешифраторов

Рис 157 Схема прямоугольного дешифратора Интегральные микросхемы преобразователей кодов, шифраторов и дешифраторов. Промышленность выпускает большое количество различных микросхем преобразователей кодов, шифраторов и дешифраторов, некоторые из которых приведены в табл. 15.3. Таблица 15.3 Интегральные микросхемы преобразователей кодов, шифраторов и дешифраторов

На базе микросхем, приведенных в табл. 15.3, возможно проектирование преобразователей кодов, шифраторов и дешифраторов различной степени сложности. Кроме приведенных специализированных микросхем иногда используют программируемые запоминающие устройства, которые применяют для вывода различных символов на экран монитора при управлении от двоичного кода. К таким элементам относятся микросхемы ПЗУ типа К155РЕ21...К155РЕ24, которые используются в качестве преобразователей двоичного кода в код русского, латинского алфавита, код арифметических и дополнительных символов. Лекция 16. Мультиплексоры и демультиплексоры Мультиплексоры. Мультиплексором называют функциональный узел, который обеспечивает передачу цифровой информации, поступающей по нескольким входным линиям связи, на одну выходную линию. Выбор входной линии, информация с которой поступает на выход, осуществляется при помощи сигналов, поступающих на адресные входы. Обобщенная схема мультиплексора приведена на рис. 16.1. Мультиплексор MUX (Multiplexer) в общем случае можно представить в виде коммутатора, управляемого входной логической схемой. Входные логические сигналы X, поступают на входы коммутатора и через коммутатор передаются на выход Y. Управление коммутатором осуществляется входной логической схемой. На вход логической схемы подаются адресные сигналы A,, (Adress). Мультиплексоры могут иметь дополнительный управляющий вход Е (Enable), который может выполнять стро-бирование выхода Y. Кроме этого некоторые мультиплексоры могут иметь выход с тремя состояниями: два состояния 0 и 1 и третье состояние — отключенный выход (выходное сопротивление равно бесконечности). Перевод мультиплексора в третье состояние производится сигналом ОЕ (Output Enable). Большинство мультиплексоров способно передавать сигналы информации X, только в одном направлении — от входа на выход. Однако имеются мультиплексоры, которые могут передавать информационные сигналы в обоих направлениях. Такие мультиплексоры называются двунаправленными. Двунаправленные мультиплексоры способны передавать не только цифровые, но и аналоговые сигналы. В литературе такие мультиплексоры часто называют селекторами-мультиплексорами (Data Selector-Multiplexer).

Рис. 16 1. Обобщенная схема мультиплексора Мультиплексоры со стробирующим входом Е выполняют функции передачи сигнялов х,—>-у только при поступлении сигнала строба Е. Мультиплексоры, имеющие три состояния выхода, можно каскадировать. Для обозначения коммутационных возможностей мультиплексора можно пользоваться условно записью (лг—^1), где п — число входов. Так, например, мультиплексор с функцией (1 —> 1) является одиночным ключом, а мультиплексор (4-*1) имеет четыре входа и один выход. В зависимости от соотношения числа информационных входов п и числа адресных входов т мультиплексоры делятся на полные и неполные. Если выполняется условие п =2", то мультиплексор будет полным. Если это условие не выполняется, т. е. п<2"1, то мультиплексор будет неполным. Наибольшее распространение получили мультиплексоры (2—1) с п=2 и т=\, (4--1) с и =4 и т=2, (8—*!) с и=8 и т=3 и (16—*1) с и=16 и т=4. Для неполных мультиплексоров число входных линий может быть любым, но, разумеется, не больше 2";. В качестве примера рассмотрим функционирование мультиплексора (4—» 1), состояние входов и выходов которого приведено в табл. 16.1. Используя таблицу состояний этого мультиплексора, получим выражение для его выходной функции

В общем виде выходная функция мультиплексора (и—*!) может быть представлена как

где К, называется мипитерм (К,=0 или 1) и равно логическому произведению сигналов на адресных линиях, соответствующих сигналу X,. Для расширения числа входных линий можно использовать каскадирование мультиплексоров. На рис. 16.2 показано пирамидальное каскадирование мультиплексоров. На этом рисунке приведен двухкаскадный мультиплексор типа (16—-I) с управлением по четырем адресным линиям А^...А^. Первая группа мультиплексоров MUXO...MUX3 управляется младшими разрядами адресных сигналов А о и А\. выходной мультиплексор MUX4 управляется старшими рязрядами адресных сигналов А-^ и Ау. Такое каскадирование мультиплексоров почти вдвое увеличивает задержку выходных сигналов. Реализация четырехвходового мультиплексора может выполняться по уравнению (16.1) или в общем случае — по уравнению (16.2). Так, например, для двувходового мультиплексора можно записать уравнение Y=Xo-Ao+X^-Ao, которое реализуется на двувходовых элементах И и ИЛИ, как показано на рис. 16.3 а. Таблица 16.1 Состояние мультиплексора (4--1)

Аналогично реализуется че-тырехвходовой мультиплексор, однако для него потребуются четыре трехвходовых элемента И и один четьгрехвходовой элемент ИЛИ Схема такого мультиплексора, построенного по уравнению (16 1), приведена на рис 16.3 б Для получения прямых и инверсных адресных сигналов используются два дополнительных инвертора Поскольку для построения мультиплексоров с большим числом входов требуются элементы И и ИЛИ с числом входов больше четырех, то их проще выполнять путем каскадирования Интегральные микросхемы мультиплексоров можно разделить на группы по следующим признакам • по числу входов 2-, 4-, 8- и 16-входовые, • по числу мультиплексоров в одном корпусе (числу разрядов), • по наличию стробирующего входа Е,

Рис 16 2 Пирамидальное каскадирование мультиплексоров (4 -* 1) для реализации выходной функции (16—*1) • по наличию выхода с тремя состояниями (наличию входа ОЕ), • по способности передавать сигналы в двух направлениях. Промышленность выпускает большое количество различных микросхем мультиплексоров, некоторые из которых приведены в табл. 16.2. Применение мультиплексоров с тремя состояниями выходов позволяет легко увеличить число коммутируемых каналов. На рис. 16.4 показана схема мультиплексора (16-* 1), выполненная на мультиплексорах (8—-1) и дешифраторе 1х2 Выходы Y мультиплексоров DD\ и DD2 соединены вместе для организации функции «монтажное ИЛИ». При значении адресного сигнала A^=Q включается микросхема DD\, а при значении A^=l — микросхема DD2. При включении микросхемы DD\ на общий выход поступает один из информационных сигналов Ху x^, подключенных к входам DDI. При включении микросхемы DD2 на общий выход поступают сигналы Ху..х^. В качестве элементов DDI и DD2 в этой схеме можно использовать интегральные микросхемы КР531КП15 (или более медленные ИМС К555КП15) Другой способ каскадирования ИМС мультиплексоров основан на использовании пирамидальной схемы, приведенной на рис. 16.2. Если взять восемь

Рис. 163. Выполнение мультиплексора (2—1) (а) и (4-*1) (б) на элементах И и ИЛИ мультиплексоров (8-*!), не имеющих третьего состояния выхода (например, К555КП7), на их адресные входы Ац.-.А^, подать одни и те же адресные сигналы, производящие выбор одного из восьми каналов в каждом мультиплексоре, то общее число входов будет равно 64 (рис. 16.5). Последний мультиплексор DD9 управляется адресными сигналами А^, Ац, А., и определяет, какой из восьми мультиплексоров DDI...DDS будет подключен к выходу Y. Вход стробирования Е можно использовать только у последнего мультиплексора DD9. Таким образом, на рис. 16.5 показана схема стробируемого мультиплексора с форматом (64-*1). Помимо основного назначения коммутации входных сигналов мультиплексоры находят применение в сдвигающих устройствах, делителях частоты, триггер-ных устройствах и др. Демультиплексоры. Демультиплексором (DMX) называют функциональный узел, который обеспечивает передачу цифровой информации, поступающей по одной линии, на несколько выходных линий. Выбор выходной линии осуществляется при помощи сигналов, поступающих на адресные входы. Таким образом, демультиплексор выполняет преобразование, обратное действию мультиплексора. Обобщенная схема демультиплексора, приведенная на рис. 16.6, сходна со схемой мультиплексора. Входной сигнал х поступает на вход коммутатора и через него передается на выходы Yy...Yn. Адресные сигналы Ay...Ai, имеют то же Таблица 16 2 Интегральные микросхемы мультиплексоров

|