Цель работы

Изучение принципов и режимов работы счетных схем и регистров. Приобретение навыков синтеза и анализа счетных схем и регистров.

Порядок выполнения работы.

1. Исследование двоичного счетчика. Счетные схемы относятся к последовательностным ЦУ, состояние выходов которых изменяется под воздействием сигнала на счетном входе в зависимости от сигналов на управляющих входах. Условное обозначение счетчика показано на рис.7.1. Одним из основных параметров счетчика является модуль счета М, численно равный количеству импульсов, необходимых для перевода счетчика в исходное состояние (до поступления счетных импульсов).

Рис.7.1

Модуль счета также характеризует емкость счетчика – число возможных его состояний. Перевод счетчика из одного состояния в другое (режим счета) обеспечивается основными элементами счетной схемы – триггерами. Выходы триггеров являются выходами счетчика, и их количество определяет его разрядность. Разряд (выход) счетчика, переключающийся чаще других по каждому входному импульсу на счетном входе, является младшим, а разряд, переключающийся реже – старшим. Счетчик может работать в режиме увеличения выходного кода. Это так называемый режим прямого счета, характерный для большинства счетных схем. В этом случае счетчик называется суммирующим и выполняет операцию инкремента. Счетчик также может работать в режиме уменьшения выходного кода. Это так называемый режим обратного или инверсного счета. В этом случае счетчик называется вычитающим и выполняет операцию декремента. Обе операции – инкремента и декремента – выполняют реверсивные счетчики в зависимости от состояния управляющих входов. 1.1. Исследование асинхронного двоичного счетчика. Асинхронные счетчики (счетчики с последовательным переносом) представляют собой цепочку последовательно включенных триггеров, работающих в счетном режиме. Асинхронными они называются потому, что каждый следующий разряд счетчика переключается с задержкой относительно предыдущего. В суммирующем счетчике последующий разряд (прямой выход) переключается при переходе предыдущего в направлении из 1 в 0, а в вычитающем – наоборот. Поэтому, при синтезе суммирующего асинхронного счетчика, работающего по переднему фронту счетных (тактовых) импульсов (например для D-триггеров), счетный вход каждого последующего разряда нужно соединить с инверсным выходом предыдущего разряда, а в вычитающем счетчике – с прямым выходом. Синтез счетчика, работающего по заднему фронту счетных импульсов (например для JK-триггеров) проводится по обратной схеме. 1.1.1 Соберите схему суммирующего асинхронного счетчика на D-триггерах (рис7.2). Для этого из библиотеки Multisim выберите D -триггеры с прямым динамическим тактовым входом (группа Misc Digita, семейство TIL, компонент D _FF ).

Рис.7.2 Подавайте на счетный вход схемы с помощью ключа тактовые импульсы и наблюдайте состояние счетчика на индикаторе. 1.1.2. Подключите к входу С счетчика вместо ключа функциональный генератор. К выходам схемы параллельно индикатору индикатор 16-ричных слов подключите. логический анализатор. Установите параметры генератора: форму импульсов – прямоугольные, частоту импульсов 10Гц. В окне логического анализатора задайте параметры развертки: установите масштаб Время/Дел – 5, затем откройте окно установок синхронизации и установите в нем тактовую частоту 30 Гц. Остальные параметры оставьте без изменения. Включите схему. и наблюдайте состояние счета на индикаторе. В результате наблюдения установите модуль счета и зарисуйте временные диаграммы на выходах счетчика за цикл счета. Запишите, по какому фронту (переднему или заднему) сигнала на входе С переключается триггеры счетчика. Сделайте выводы.

1.1.3. Соберите схему вычитающего 3- разрядного асинхронного счетчика на D-триггерах, используя сведения о нем в п.1.1, и по аналогии с п.1.1.1. В результате наблюдения за работой счетчика установите его модуль счета и зарисуйте временные диаграммы на выходах за цикл счета. Сравните результаты работы по схемам суммирующего и вычитающего счетчиков, сделайте выводы. Запишите отличительные признаки обеих схем. 1.1.4. Соберите схему суммирующего 4- разрядного асинхронного счетчика на JK-триггерах. Из библиотеки Multisim выберите JK-триггер с прямым динамическим тактовым входом (группа Misc Digita, семейство TIL, компонент JK_FF). (рис.7.4).

Рис.7.4 Для работы триггеров схемы в счетном режиме J- и K входы должны быть подключены к источнику логической 1 (объясните почему). Обратите внимание, что на свободных прямых RS-входах присутствуют пассивные нулевые логические уровни, и для нормальной работы схемы эти входы можно не подключать. Для освобождения рабочей области от связей и для приобретения навыков используйте шины (как на рис 7.4). Подавайте на счетный вход схемы с помощью ключа тактовые импульсы и наблюдайте состояние счета на индикаторе. 1.1.5. Подключите к входу С счетчика вместо ключа функциональный генератор. К выходам схемы параллельно индикатору индикатор 16-ричных слов подключите. логический анализатор. Установите параметры генератора: форму импульсов – прямоугольные, частоту импульсов 10Гц. В окне логического анализатора задайте параметры развертки: установите масштаб Время/Дел – 5, затем откройте окно установок синхронизации и установите в нем тактовую частоту 30 Гц. Остальные параметры оставьте без изменения. Включите схему. и наблюдайте состояние счета на индикаторе. В результате наблюдения установите модуль счета и зарисуйте временные диаграммы на выходах счетчика за цикл счета. Запишите, по какому фронту (переднему или заднему) сигнала на входе С переключается триггеры счетчика. Сделайте выводы. Сравните временные диаграммы работы суммирующегоасинхронного счетчика на D-триггерах и на JK-триггерах и по результатам сравнения сделайте выводы. 1.1.6. Синтез схемы делителя частоты с коэффициентом деления Кд , не равным модулю счета. 1.1.6.1. Схема делителя частоты строится по принципу асинхронного суммирующего счетчика. Для синтеза схемы необходимо соблюдать условие 2n ≥ Кд, где 2n – модуль счета, n - число триггеров в схеме. Например, для Кд = 3 число триггеров равно двум, так как 22= 4, а для Кд = 9 число n равно четырем, так как 23< 9 < 24. На рис.7.5 показан пример построения делителя частоты с Кд = 9. Схема состоит из асинхронного счетчика на D- триггерах и комбинационной схемы на ЛЭ типа 2И (так называемая схема совпадения). Кд схемы равно 16, т.е. модулю асинхронного счетчика, построенного на 4-х D - триггерах, т.к. 24= 16. Для получения Кд= 9 необходимо изменить (уменьшить) модуль счета путем обнуления всех разрядов в момент прихода 9-го импульса.

Рис.5 Для этого рассмотрим состояние выходов, соответствующее десятичному числу 9: 910= 10012, т.е. Q3=1; Q2=0; Q1=0; Q0=1. То есть, ко входам схемы совпадения следует подключить прямые выходы 0-го и 3-го разрядов счетчика и инверсные выходы 1-го и 2-го разрядов. А для организации сброса триггеров в нулевое состояние в момент прихода 9-го импульса необходимо в этот момент подать активный сигнал сброса с выхода схемы совпадения на соответствующие входы триггера. Например, если D –триггер имеет прямые RS-входы, то активным сигналом для таких входов является логическая единица. Поэтому в момент прихода 9-го импульса необходимо подать на RS-входы всех триггеров логическую единицу. Если D –триггер имеет инверсные RS-входы, то активным сигналом для таких входов является логический ноль. Поэтому в момент прихода 9-го импульса необходимо подать на RS-входы всех триггеров логический ноль 1.1.6.2. Соберите схему делителя частоты на D- триггерах или JK-триггерах (по заданию преподавателя) с Кд = 5. К выходам схемы подключите логический анализатор и индикатор. Включите схему. В результате наблюдения за работой делителя частоты зарисуйте временные диаграммы на выходах. 1.2. Исследование синхронного двоичного счетчика. В синхронных счетчиках (счетчиках с параллельным переносом) тактовые импульсы поступают на счетные входы триггеров одновременно. В общем случае такая схема состоит из ряда триггеров, количество которых определяется разрядностью счетчика и вспомогательной комбинационной схемы. Последняя обеспечивает заданный переход счетчика из предыдущего состояния в следующее. Структура синхронной счетной схемы показана на рис.7.6.

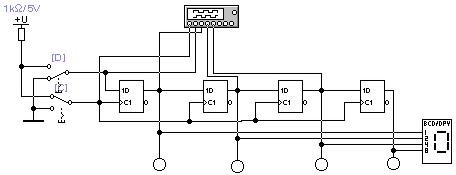

Рис.7.6 В качестве триггеров обычно используют универсальные J-K триггеры либо D-триггеры. 1.2.1. Опишите синтез синхронного счетчика, считающего от 0 до 5 циклически. Для синтеза выберите, например, D-триггеры. 2. Исследование регистров. Регистры служат для приема (записи), хранения, выдачи (считывания), сдвига информации, представленной многоразрядным двоичным кодом. По способам записи-считывания регистры делятся на параллельные (статические), в которых информация обрабатывается в параллельной форме (N входов данных и N выходов), последовательные (сдвигающие), имеющие один вход данных и один выход, и последовательно- параллельные. Регистры строят, так же как и счетные схемы на триггерах (в основном на D-триггерах с динамическим управлением). Как правило, число разрядов регистра 4 или 8. 2.1. Синтез схемы параллельного 2-х разрядного регистра. В параллельном регистре число триггеров соответствует числу разрядов входного слова. На выход регистра это слово переписывается по сигналу синхронизации на счетных входах всех триггеров. Соберите схему, изображенную на рис.7.12.

Рис.7.12 Включите схему и исследуйте ее работу: подавайте с помощью ключа сигналы синхронизации и наблюдайте с помощью логического анализатора сигналы на входах и выходах. Зарисуйте временные диаграммы. Проанализируйте их, сделайте выводы. 2.2. Синтез схемы последовательного 4- разрядного регистра. В последовательном (сдвигающем) регистре число триггеров равно разрядности входного слова (так же, как и в параллельном регистре). Входной код подается поразрядно, начиная со старшего разряда на левый триггер регистра. При этом ввод каждого разряда слова производится по синхронизирующему импульсу на счетных входах всех триггеров. В результате в каждом последующем триггере формируется и запоминается сигнал от предыдущего. Таким образом, для записи числа в регистр и для заполнения всех его N триггеров необходимо подать N синхроимпульсов. Соберите схему, изображенную на рис.7.13. Рассмотрим пример ввода в регистр 4 - разрядного слова 1010, десятичный эквивалент которого соответствует числу 10. Сначала на вход регистра (на левый триггер) подается значение старшего разряда слова, т. е. 1. Для этого ключ D нужно перевести в верхнее положение, подключив вход левого триггера к источнику логической 1.

Рис.7.13

Затем на счетный вход С всех триггеров подается синхронизирующий импульс. Для этого ключ С переводится из положения логического 0 в 1 (из нижнего положения в верхнее), так как известно, что D-триггер срабатывает по фронту импульса синхронизации. Значение следующего разряда входного кода - 0 – вводится в регистр аналогично, но ключ D при этом необходимо перевести вниз, подключив вход левого триггера к источнику логического 0. В результате ввода слова на цифровом индикаторе отобразится шестнадцатиричный его эквивалент. Выполните данный пример, и по показаниям логических пробников заполните табл.7.1, полагая, что выход О0 соответствует младшему разряду регистра (левому триггеру), а выход О3 – старшему (правый крайний триггер). Проанализируйте таблицу и сделайте выводы о направлении сдвига информации в регистре (вправо или влево). Также сделайте выводы о направлении изменения числа на индикаторе (увеличивается или уменьшается) при подаче на вход D только логической 1 или 0. Создайте подсхему регистра. Введите в регистр последовательно другие числа, например, 5, 7, 12, продолжая заполнять табл.7.1 (с 5-го по 8-й такты для числа 5; с 9-го по 12-й такты для числа 7; и с 13 по16-й такты для числа 12). Убедитесь в правильности ввода чисел по показаниям цифрового индикатора и в направлении сдвига информации в регистре. Таблица 7.1

2.3. Синтез регистра Джонсона. Если в схеме на рис.13 вход D левого крайнего триггера отсоединить от ключа D и подключить к инверсному выходом правого, то получим регистр Джонсона. Выполните синтез этого регистра. Включите схему. Подавайте с помощью ключа С синхронизирующие импульсы, наблюдайте за состоянием логических пробников и индикатора. Заполните таблицу 7.2, зафиксировав в ней состояние регистра Джонсона за 8 тактов. Проанализируйте таблицу, сделайте выводы о направлении сдвига информации в регистре. На основе сравнения таблиц 1 и 2. опишите принципиальные схемотехнические отличия, и, как следствие, отличия в работе обеих схем.

|