Назначение и принцип формирования виртуальных контейнеров VC в модуле STM-1. Структура VС-12.

Плезиохронные потоки со скоростями 2.048 Мбит/с, формируемые, например, на выходе аппаратуры ИКМ 30, широко распространены в современных сетях. Поток 2.048 Мбит/с содержит в своем составе 32 канальных интервала, каждый из которых имеет 8 разрядов или один байт, то есть 32 байта на периоде 125 мкс. Согласно редакции Европейского института стандартов (ETSI), поток PDH со скоростью 2.048 Мбит/с предварительно размещается в контейнере C12. Под термином “размещение” понимают то, что цифровой поток PDH размещается на определенных позициях байтов этого контейнера. Контейнер C12 представляет из себя структуру элементарного временного цикла, состоящего из информационных битов и битов контроля аппаратуры асинхронной сети со скоростью передачи 2.048 Мбит/с. Структура контейнера представляется в виде матрицы полезной нагрузки и содержащей 140 байт. Байты организованны в 4 цикла протяженностью 125 мкс каждый, образуя, таким

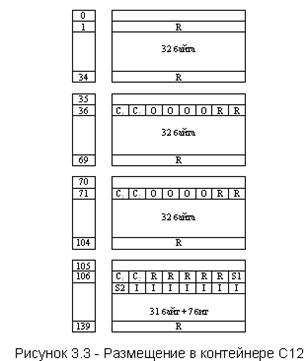

образом, сверхцикл длительностью 500 мкс. Структура контейнера C12 приведена на рисунке 3.2. Байты, обозначенные номерами 0, 35, 70 и 105, относящиеся к структуре контейнера C12, отведены под трактовый заголовок (Path Overhead, POH), виртуального контейнера VC12. На рисунке 3.3 байты представлены в последовательной форме, что позволяет лучше оценить размещение информации в матрице полезной нагрузки. Чтобы компенсировать различие в скоростях поступающего цифрового потока (2,048 Мбит/с) и сигнала, относящегося к контейнеру С12, необходимо осуществлять процедуру выравнивания (согласования) скоростей, которая заключается в доведении скорости передачи ЦП до некоторой номинальной скорости в структуре C12. Процедура согласования скоростей осуществляется путем введения в цифровой сигнал дополнительных (выравнивающих) символов. С этой целью в структуре C12 предусмотрены, биты C1 и С2, указывающие на наличие или отсутствие согласования скоростей. Эти биты могут принимать следующие значения: C1=1; C2=1 – положительное выравнивание. C1=0; С2=0 – отрицательное выравнивание. C1=0; С2=1 – нет выравнивания. Биты S1 и S2, указывают на вид согласования скоростей. S1 – бит исключаемый из передачи при отрицательном выравнивании. S2 – балластный бит при положительном выравнивании.

I: информационные биты; R: фиксированный стаффинг; О: дополнительный бит (Overhead); C: управление выравниванием; S: возможное выравнивание. При формировании виртуального контейнера VC12 вводится поле сверхцикла, который объединяет 4 контейнера C12. При этом добавляются служебные байты. Таким образом, структура VC12 состоит из полезной нагрузки, сформированной в контейнере C12, и присоединенных к ней служебных байт, которые получили название заголовка (Overhead). Размер контейнера VC12 равен 140 байтам, при длительности сверхцикла 500 мкс. Дополнительные байты трактового заголовка POH используют четыре байта V5, J2, Z6 т K4. Существуют три способа ввода нагрузки в VC12:

В первом случае контейнер VC12 образован из 1023 битов (127 байт + 7 бит). Два бита для возможного выравнивания (justification opportunity), один для положительного выравнивания (S2), другой – для отрицательного (S1), шесть битов для управления выравниванием (С1 и C2), один байт POH, восемь дополнительных каналов (биты О), использование которых не определено, и 72 резервных бит (8 байтов – 5R, J2, Z6, K4 и 8 битов R). Выравнивание, которое здесь используется, предназначено для синхронизации сигнала PDH в соответствии с тактовой частотой сети SDH. Его цель заключается в компенсации разности частот в пределах сети SDH. В случае размещения бит – синхронного сигнала 2.048 Мбит/с, выравнивание не требуется, поскольку сигнал синхронизирован от оборудования SDH. Один бит возможного выравнивания (S2) всегда несет информацию, а другой (S1) становится стаффинг – битом. Управляющие биты имеют фиксированные значения “0” и ”1”. Из более поздних рекомендаций бит – синхронное размещение исключено, так как это частный случай размещения асинхронного сигнала 2.048 Мбит/с, и тот же мультиплексор может выполнить это размещение без использования какого – либо другого процесса. Размещение байт – синхронного сигнала 2.048 Мбит/с в VC12 применяется, когда в сигнале SDH необходима возможность распознавания индивидуальных каналов 64 Кбит/с потока 2.048 Мбит/с.

Рисунок 3.4 - Размещение сигнала 2М в VC12 P: цикловой синхросигнал; M: сверхцикловой синхросигнал; V5: байт трактового заголовка (POH); J2: байт контроля исправности VC12; Z6: байт повышения качества связи; K4: резервный байт.

|