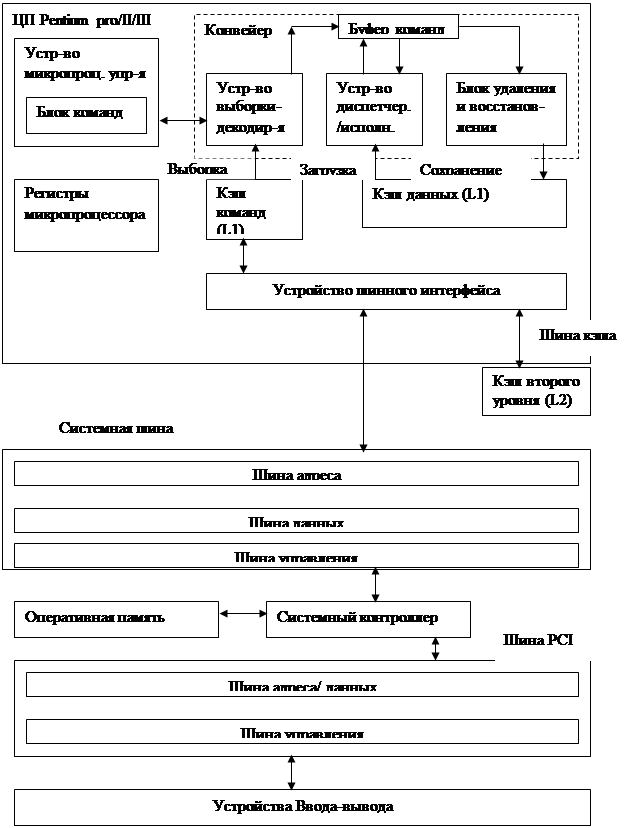

Особенности архитектуры PENTIUM Intel Р6.

На рис. показана схема компьютера на базе микропроцессоров семейства Intel Р6. Все современные ЭВМ обладают некоторыми общими индивидуальными свойствами архитектуры, называемой фон-неймановской. Напомню их: 1. Принцип хранимой программ ы, согласно которому код программы и ее данные находятся в одном адресном пространстве в оперативной памяти; 2. Принцип микропрограммирования, согласно которому машинные команды подразделяются на действия-сигналы, которые в определенном порядке должны быть выполнены для осуществления преобразований, предполагаемых машинной командой. Вследствие этого, в микропроцессор входит блок микропрограммного управления; 3. Линейное пространство памяти, согласно которому ячейкам оперативной памяти присваиваются последовательные номера (адреса) 1.2… и т.д.; 4. Последовательное выполнение программы, согласно которому команды выбираются из памяти микропроцессором последовательно, изменить этот порядок могут только команды перехода; 5. Отсутствие отличия между командами и данными. Микропроцессор, исполняя содержимое некоторой последовательности ячеек памяти всегда трактует их как машинную команду, и если это не так, происходит аварийное завершение программы. Поэтому в программе важно разделять пространства программы и данных, чему способствует выделение в программе на Ассемблере сегментов программы и данных. 6. Безразличие к целевому назначению данных. Микропроцессору безразлично какую смысловую нагрузку несут обрабатываемые данные, за правильную интерпретацию данных ответственность несет программист. Имея перечисленные архитектурные свойства, микропроцессор Intel Р6 обладает некоторыми индивидуальными особенностями: 1. Суперскалярная архитектура. Чтобы уяснить этот термин необходимо прежде поныть значение термина конвейеризация вычислений. Важным элементом архитектуры, появившимся в i486, является конвейер – специальное устройство, реализующее обработку команд внутри процессора в несколько этапов. Вышеупомянутый конвейер имеет 5-ти ступенчатый конвейер. Соответствующие этапы включают: - выборку команд из кэш-памяти или оперативной памяти; - декодирование команды; - генерацию адреса, в процессе которой определяются адреса операндов в памяти; - выполнение операции с помощью АЛУ (арифметико-логического устройства); - запись результаты (адрес определяется конкретной машинной командой). Каждому этапу соответствует своя схема в составе конвейера. Поэтому, когда после выборки команда поступает в блок декодирования, блок выборки оказывается свободным и может обрабатывать следующую команду. Таким образом, на конвейере могут находиться в разной стадии выполнения 5 команд, в результате чего возрастает скорость обработки отдельной команды. Микропроцессоры, имеющие один конвейер называются скалярными, а более одного – суперскалярными. Микропроцессор Pentium имеет два конвейера, и поэтому может выполнять 2 команды за машинный такт. 2. Раздельное кэширование кода и данных. Кэширование – это способ увеличения быстродействия ЭВМ за счет хранения часто используемых данных и кодов в так называемой кэш-памяти первого уровня (быстрой памяти), находящейся внутри микропроцессора. Как видно из схемы, Intel Р6 содержит 2 блока кэш-памяти, один для кодов, а другой – для данных. Объем каждого блока по 8 Кбайт памяти. За счет одновременного доступа к быстрой памяти кодов и данных возрастает скорость работы компьютера. 3. Предсказание правильного адреса перехода. Под переходом понимается запланированное алгоритмом изменение последовательного выполнения команд. Статистика показала, что на каждые 6-8 команд приходится 1 команда безусловного или условного перехода. Это обстоятельство приводит к тому, что через каждые 6-8 команд конвейер команд нужно очищать и вводить в него новую последовательность, что может свести на нет преимущества конвейеризации. Поэтому в Pentium был введен блок предсказания переходов. Для предсказания Pentium имеет буфер адресов переходов, который хранит информацию о последних 256 переходах программы. Если некоторая команда управляет ветвлением, то в буфере запоминается эта команда, адрес перехода и предположение о том, какая ветвь программы будет выполняться следующей. Почти ни одна программа не может обойтись без циклов, в ходе выполнения которых периодически принимается решение либо о выходе из цикла. Либо о переходе на его начало. Специальный блок предсказания адреса перехода прогнозирует, какое решение будет принято программой при следующем выполнении цикла. Нетрудно понять, что в цикле по счетчику следующим будет переход на начало цикла при значениях счетчика, больших 1. Труднее предсказать переход в циклах с дополнительными условиями, но даже прогноз, аналогичный простому циклу оправдывается в большинстве случаев. Эффективность этого нововведения в архитектуру ЭВМ можно оценить по тому, что вероятность правильного предсказания составляет 80%. Наиболее ценным нововведением архитектуры Pentium Р6 является реализация механизма интеллектуальной обработки потока команд, получившего название “динамического выполнения”. Этот механизм основывается на следующих свойствах, которые уже существовали в прежних моделях микропроцессоров Intel, но были усовершенствованы. 1. Предсказание переходов, в том числе и вложенных. В Pentium Р6 этот механизм реализуется устройством выборки-декодирования и имеет основной целью исключение перезагрузки конвейера. 2. Динамический анализ потока данных. Анализ проводится с целью определения зависимостей команд от данных и регистров процессора с последующей оптимизацией потока выполняемых команд. Главный критерий – максимальная загрузка конвейера. Требование выполнения этого критерия приводит в некоторых случаях к нарушению последовательности выполнения команд, поступающих на конвейер. (Вообще-то это новшество нарушает один из принципов программного управления!) Такое отступление от основополагающего принципа осуществляется в тех случаях, когда для очередной команды нет данных нив кэш-памяти первого, ни в кэш памяти второго уровня. В этих случаях требуется “подкачка информации” из оперативной памяти в быструю, а чтобы конвейер не простаивал во время подкачки, ищется и выполняется команда, для которой информация есть в быстрой или регистровой памяти. 3. Интеллектуальное исполнение. Этим термином называется способность микропроцессора организовать неупорядоченное выполнение команд и восстановления впоследствии порядка за счет передачи результатов выполнения команд в порядке, предусмотренном алгоритмом обработки данных. Для реализации этого механизма результаты выполнения находящихся на конвейере команд размещаются во временных регистрах (буфер команд). Блок удаления и восстановления постоянно просматривает буфер команд и ищет те из них, которые уже исполнены и не имеют связи по данным с другими командами или не находятся в ветвях незавершенных переходов. Когда такие команды найдены, устройство удаления и восстановления помещает сформированные ими данные в память или регистры процессора в порядке, заданным исходным алгоритмом. После этого команды удаляются из конвейера. Механизм динамического выполнения команд приводит к тому, что наиболее оптимально используется время наиболее дорогостоящего компонента ЭВМ – микропроцессора, а если учесть, что в последних версиях Pentium команды программы исполняются в 3 потока одновременно, то понятным становятся истоки повышения производительности, достигаемые в этих моделях. Чтобы понять современные тенденции в архитектуре ЭВМ необходимо рассмотреть две конкурирующие идеи: конвейеризации и параллелизма. Надеюсь, идея параллелизма после рассмотрения архитектуры Pentium Р6 в общих чертах Вам стала понятной.

|