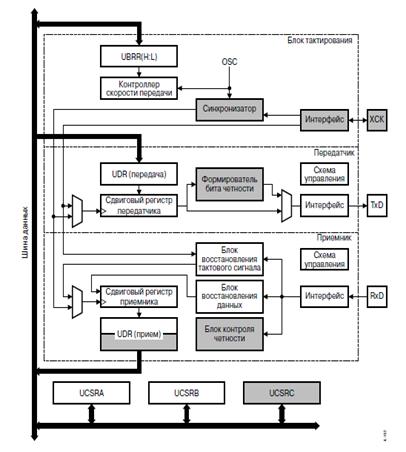

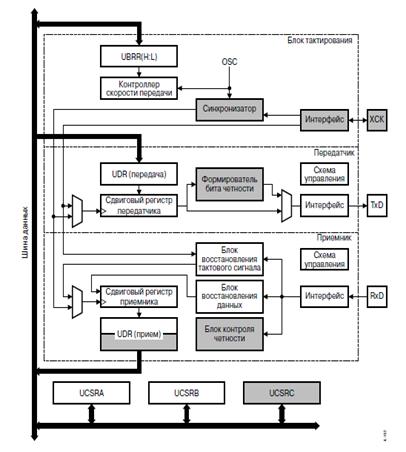

Упрощенная структурная схема одного модуля USART приведе на Рис.8.1.

Рис.81. Структурная схема модуля USART

Как показано на рисунке, модуль состоит из трех основных частей: блока тактирования, блока передатчика и блока приемника. Блок тактирования модулей USART включает в себя схему синхронизации, которая используется при работе в синхронном режиме и контроллер скорости передачи.

Блок передатчика включает одноуровневый буфер, сдвиговый регистр,схему формиро- вания бита четности и схему управления.Блок приемника, в свою очередь, включает схемы восстановления тактового сигнала и данных, схему контроля четности, двухуровневый, сдвиговый регистр, а также схему управления.

Буферные регистры приемника и передатчика располагаются по одному адресу пространства ввода/вывода и обозначаются как регистр данных UDR (Universal Data Register) (UDR n). В этом регистре хранятся младшие 8 разрядов принимаемых и передаваемых данных. При чтении выполняется обращение к буферному регистру UDR приемника, при записи — к буферному регистру передатчика. Размещение регистров данных UDR приведено в Табл.8.2.

Таблица 8.2 Размещение регистров данных модулей USART

| Регистр

| Адрес

| Описание

|

| UDR0

| $0C ($2C)

| Регистр данных

USART0

|

| UDR1

| ($9C)

| Регистр данных

USART1

|

В модулях USART буфер приемника является двухуровневым (FIFO_буфер), изменение состояния которого происходит при любом обращении к регистру UDR. Для управления модулями USART используются три регистра: UCSRA (UCSR n A), UCSRB (UCSR n B) и UCSRC (UCSR n C). Адреса этих регистров указаны в Табл.8.3.

Таблица 8.3. Регистры управления и состояния модулей USART

| Регистр

| Адрес

| Описание

|

| UCSR0A

| $0B ($2B)

| Регистр управления A

USART0

|

| UCSR0B

| $0A ($2A)

| Регистр управления B

USART0

|

| UCSR0C

| ($95)

| Регистр управления C

USART0

|

| UCSR1A

| ($9B)

| Регистр управления A

USART1

|

| UCSR1B

| ($9A)

| Регистр управления B

USART1

|

| UCSR1C

| ($9D)

| Регистр управления C

USART1

|

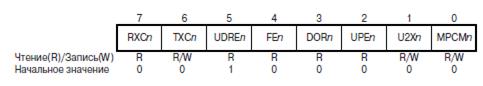

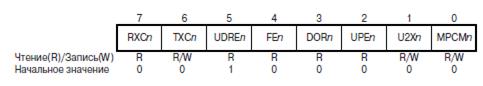

Формат регистров UCSRA (UCSR n A), UCSRB (UCSR n B) и UCSRC (UCSR n C) приведен на Рис.8.2 …8.4 а значение разрядов этих регистров описано в Таблице 8.9….8.11 соответственно.

Рис.8.2. Формат регистров UCSRA, UCSR0A и UCSR1A

Таблица 8.4.. Разряды регистров UCSR0A и UCSR1A

| Разряд

| Название

| Описание

|

|

| RXC n

| Флаг завершения приема.Флаг устанав- ливается в «1» при наличии непрочитанных данных в буфере приемника (регистр данных UDR). Сбрасывается флаг аппаратно после опустошения буфера. Если разряд RXCI n ре- гистра UCSR n B установлен, то при установке флага генерируется запрос на прерывание «прием завершен

|

|

| TXC n

| Флаг завершения передачи.Флаг устанавливается в «1» после передачи всех разрядов посылки из сдвигового регистра передатчика, при условии, что в регистр данных UDR не было загружено нового значения. Если разряд TXCIE регистра UCSR n B установлен, то при установке флага генерируется прерывание «передача завершена». Флаг сбрасы вается аппаратно при выполнении подпрограммы обработки прерывания или программно, записью в него лог. 1

|

|

| UDRE n

| Флаг опустошения регистра данных.Данный флаг устанавливается в «1» при пустом буфере передатчика (после пересылки байта из регистра данных UDR в сдвиговый регистр передатчика). Установленный флаг означает, что в регистр данных можно загружать новое значение. Если разряд UDRIE регистра UCSRB установлен, гене рируется запрос на прерывание «регистр данных пуст». Флаг сбрасывается аппаратно, при записи в регистр данных

|

|

| FE n

| Флаг ошибки кадрирования.Флаг устанавливается в «1» при обнаружении ошибки кадрирования, т. е. если первый стоп_бит принятой посылки равен «0». Флаг сбрасывается при приеме стоп_бита, равного «1»

|

|

| DOR n

| Флаг переполнения.В USART флаг устанавлива- ется в «1», если в момент обнаружения нового старт_бита в сдвиговом регистре приемника нахо дится последнее принятое слово, а буфер прием ника полон (два значения).. Флаг сбрасыва ется при пересылке принятых данных из сдвигового регистра приеника в буфер

|

Продолжение таблицы 8.4

| Разряд

| Название

| Описание

|

|

| UPE n

| Флаг ошибки контроля четности.Флаг устанав- ливается в «1», если в данных, находящихся в буфе- ре приемника, выявлена ошибка контроля чет ности. При отключенном контроле четности этот разряд постоянно сброшен в «0»

|

|

| U2X n

| Удвоение скорости обмена.Если этот разряд уста- новлен в «1», коэффициент деления предделителя контроллера скорости передачи уменьшается с 16 до 8, удваивая тем самым скорость асинхронного обме- на по последовательному каналу. В USART разряд U2X n используется только при асинхронном режиме работы. В синхронном режиме он должен быть сброшен

|

|

| MPCM n

| Режим мультипроцессорного обмена.Разряд MPCM используется в режиме мультипроцессорного обмена. Если он установлен в «1», ведомый микро -контроллер ожидает приема кадра, содержащего адрес. Кадры, не содержащие адреса устройства, игнорируются

|

Примечание: n 0 для UCSRA0 и 1 для UCSRA1

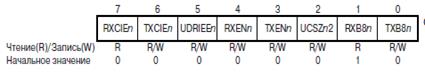

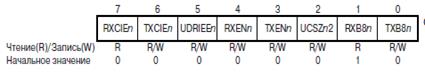

n - 0 для UCSR0В, 1 для UCSR1В

Рис. 8.3 Формат регистров UCSR0B и UCSR1B

Таблица 8.5. Разряды регистров UCSR0B и UCSR1B

| Разряд

| Название

| Описание

|

|

| RXCIE n

| Разрешение прерывания по завершению приема.Если данный разряд установлен в «1», то при установ ке флага RXC n регистра UCSR n A генериру ется пре- рывание «прием завершен» (если флаг I регистра SREG установлен в «1»)

|

|

| TXCIE n

| Разрешение прерывания по завершению передачи.Если данный разряд установлен в «1», то при установ- ке флага TXC n регистра UCSR n A генерируется пре- ры вание «передача завершена» (если флаг I регистра SREG уста- новлен в «1»)

|

|

| UDRIE n

| Разрешение прерывания при очистке регистра данных.Если данный разряд уста- новлен в «1», то при установке флага UDRE в регистра UCSR n A генери -руется прерывание «регистр данных пуст» (если флаг I регистра SREG установлен в «1»

|

|

| RXEN n

| Разрешение приема.При установке этого разряда в «1» разрешается работа приемника USART и перео- пределяется функцио- нирование вывода RXD n. При сбросе разряда RXEN n работа приемника запре ща- ется, а его буфер сбрасывается. Значения флагов TXC n, DOR n /OR n и Fe n при этом становятся недей- ствительными

|

|

| TXEN n

| Разрешение передачи.При установке этого разряда в «1» разрешается работа передатчика UART и переоп- ределяется функционирование вывода TXD n. Если разряд сбрасывается в «0» во время передачи, выклю -чение передатчика произойдет только после заверше -ния передачи данных, находящихся в сдвиговом регист ре и буфере передатчика

|

|

| UCSZ n 2

| Формат посылок.Этот разряд используется для задания размера слов данных, передаваемых по после довательному каналу. В модулях USART он использу- ется совместно с разрядами UCSZ n 1:0 регистра UCSR n C.

|

|

| RXB8 n

| 8_й разряд принимаемых данных.При использовании 9_разрядных слов данных этот разряд содержит значе- ние старшего разряда принятого слова. В случае USART содержимое этого разряда должно быть считано до прочтения регистра данных UDR

|

|

| TXB8 n

| 8_й разряд передаваемых данных.При использова- нии 9_разрядных слов данных, содержимое этого разряда является старшим разрядом передаваемого слова. Требуемое значение должно быть занесено в этот разряд до загрузки байта данных в регистр UDR

|

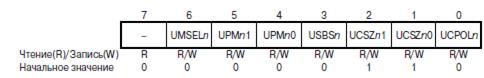

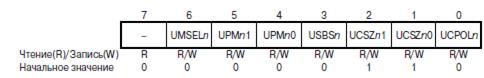

Рис.84. Формат регистров UCSR0C и UCSR1C

Таблица 8.6 Разряды регистров UCSR0C и UCSR1C

| Разряд

| Название

| Описание

|

|

| -

| Зарезервировано, читается как «0».

|

|

| UMSEL n

| Режим работы USART.Если разряд сброшен в «0», модуль USART работает в асинхронном режиме. Если разряд установ лен в «1», то модуль USART работает в синхронном режиме

|

|

| UPM n 1

| Режим работы схемы контроля и формирования четности.Эти разряды определяют функционирование схем контроля и форми рования четности

|

|

| UPM n 0

|

|

| USBS n

| Количество стоп_битов.Этот разряд определяет количество стоп_битов, посылаемых передатчиком. Если разряд сброшен в 0», передатчик посылает 1 стоп_бит, если установлен в «1», то 2 стоп_би та. Для приемника содержимое этого разряда безраз -лично

|

|

| UCSZ n 1

| Формат посылок.Совместно с разрядом UCSZ n 2 эти

Р зряды определяют количество разрядов данных в посылках (размер слова)

|

|

| UCSZ n 1

|

|

| UCPOL n

| Полярность тактового сигнала.Значение этого разряда пределяя ет момент выдачи и считывания данных на выводах модуля. Разряд ис пользуется только при работе в синхронном режиме. При работе в асинхронном режиме он должен быть сброшен в «0»

|

| UCPOL n

| Выдача данных на вы вод TXD n

| Считывание данных с

Вывода RXD n

|

|

| Спадающий фронт

XCK n

| Нарастающий фронт

XCK n

|

|

| Нарастающий фронт XCK n

| Спадающий фронт XCK n

|

Примечание: n = 0 или 1.