Функционирование модуля SPI

Структурная схема модуля SPI приведена на Рис. 9.1. Модуль SPI использует четыре вывода микроконтроллера. Как и для большинства прочих периферийных устройств, эти выводы являются линиями портов ввода/вывода общего назначения (Табл.9.1)

Рис.9.1. Структурная схема модуля SPI Таблица 9.1. Выводы, используемые модулем SPI

При включенном модуле SPI режим работы указанных выводов (направление передачи данных) переопределяется согласно Табл.9.2 Направление передачи данных определяется состоянием соответствующего разряда регистра DDRB. Таблица 9.2. Переназначение режима работы выводов модуля SPI

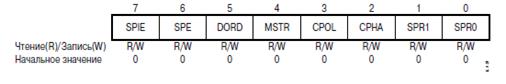

Как видно из таблицы, в определенных случаях пользователь должен самостоятельно задать режим работы вывода, используемого модулем SPI, в соответствии с его назначением (см. далее). При этом возможность управления внутренними подтягивающими резисторами выводов, работающих как входы, сохраняется независимо от способа управления их режимом работы. Для управления модулем SPI предназначен регистр управления SPCR, расположенный по адресу $0D ($2D). Формат этого регистра приведен на Рис. 9.2 а краткое описание функций разрядов регистра приведено в Табл. 9.3 Подробно использование различных разрядов регистра будет описано далее.

Рис.9.2. Формат регистра SPCR

Таблица 9.3. Разряды регистра SPCR

Контроль состояния модуля, а также дополнительное управление скоростью обмена осуществляется с помощью регистра состояния SPSR, расположенного по адресу $0E ($2E). Разряды с 7-го по 1-й этого регистра доступны только для чтения, а 0-й разряд — как для чтения, так и для записи. Формат этого регистра приведен на Рис.9.3, а назначение его разрядов описано в Табл.9.4

Рис 9.3. Формат регистра SPSR Таблица 9.4 Разряды регистра SPSR Передаваемые данные записываются, а принимаемые — считываются из регистра данных SPDR, расположенного по адресу $0F ($2F). Запись в этот регистр инициирует начало передачи, а при его чтении считывается содержимое буфера сдвигового регистра. Другими словами, регистр данных служит буфером между регистровым файлом микроконтроллера и сдвиговым регистром модуля SPI. Соединение двух микроконтроллеров (ведущий—ведомый) по интерфейсу SPI показано на Рис.9.4. Вывод SCK ведущего микроконтроллера является выходом тактового сигнала, а ведомого микроконтроллера — входом. Перед выполнением обмена необходимо, прежде всего, разрешить работу модуля SPI. Для этого следует установить в «1» разряд SPE регистра SPCR. Режим работы определяется состоянием разряда MSTR этого регистра: если разряд установлен в «1», микроконтроллер работает в режиме «Master», если сброшен в «0» — в режиме «Slave».

Рис.9.4. Соединение микроконтроллеров по интерфейсу SPI Передача данных осуществляется следующим образом. При записи в регистр данных SPI ведущего микроконтроллера запускается генератор тактового сигнала модуля SPI, и данные начинают поразрядно выдаваться на вывод MOSI и соответственно поступать на вывод MOSI ведомого микроконтроллера. Порядок передачи разрядов данных определяется состоянием разряда DORD регистра SPCR. Если разряд установлен в «1», первым передается младший разряд байта, если же сброшен в «0» — старший разряд. После выдачи последнего разряда текущего байта генератор тактового сигнала останавливается с одновременной установкой в «1» флага «Конец передачи» (SPIF). Если прерывания от модуля SPI разрешены (флаг SPIE регистра SPCR установлен в «1»), генерируется запрос на прерывание. После этого ведущий микроконтроллер может начать передачу следующего байта либо, подав на вход SS ведомого микроконтроллера напряжение ВЫСОКОГО уровня, перевести последний в состояние ожидания. Одновременно с передачей данных от ведущего к ведомому происходит передача и в обратном направлении при условии, что на входе SS ведомого присутствует напряжение НИЗКОГО уровня. Таким образом, в каждом цикле сдвига происходит обмен данными между устройствами. Аналогично в конце каждого цикла флаг SPIF устанавливается в «1» как в ведущем микроконтроллере, так и в ведомом. Принятые байты сохраняются в приемных буфрах для дальнейшего использования. В модуле реализована одинарная буферизация при передаче и двойная при приеме. Это означает, что готовый для передачи байт данных не может быть записан в регистр данных SPI до окончания предыдущего цикла обмена. При попытке изменить содержимое регистра данных во время передачи устанавливается в «1» флаг WCOL регистра SPSR. Сбрасывается этот флаг после чтения регистра SPSR с последующим обращением к регистру данных SPI. Соответственно, при приеме данных принятый байт должен быть прочитан из регистра данных SPI до того, как в сдвиговый регистр поступит последний разряд следующего байта. В противном случае первый байт будет потерян.

|