Прием данных

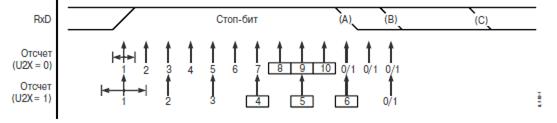

Работа приемника разрешается установкой разряда RXEN n регистра UCSR n B. При установке разряда вывод RXD n подключается к приемнику USART и начинает функциони- ровать как вход независимо от установок регистров управления портом. Если используется синхронный режим работы, переопределяется также функционирование вывода XCK n. Прием данных начинается сразу же после обнаружения приемником корректного старт_бита. Каждый разряд содержимого кадра затем считывается с частотой, определяемой установками контроллера скорости передачи или тактовым сигналом XCK (XCK n). Считанные разряды данных последовательно помещаются в сдвиговый регистр приемника до обнаружения первого стоп_бита кадра. После этого содержимое сдвигового регистра пересылается в буфер приемника, из которого принятое значение может быть получено путем чтения регистра данных модуля. При использовании 9_разрядных слов данных значение старшего разряда может быть определено по состоянию флага RX8 n регистра UCSR n B. Причем в модулях USART содержимое старшего разряда данных должно быть считано до обращения к регистру данных. Это связано с тем, что флаг RX8 n отображает значение старшего разряда слова данных кадра, находящегося на верхнем уровне буфера приемника, состояние которого при чтении регистра данных изменится. Если во время приема кадра была включена схема контроля четности, она вычисляет бит четности для всех разрядов принятого слова данных и сравнивает его с принятым битом четности. Результат проверки запоминается в буфере приемника вместе с принятым словом данных и стоп_битами. Наличие или отсутствие ошибки контроля четности может быть затем определено по состоянию флага UPE n. Этот флаг устанавливается в «1», если следующее слово, которое может быть прочитано из буфера, имеет ошибку контроля четности. При выключенном контроле четности флаг UPE n всегда читается как «0». Блок приемника модулей USART имеет еще два флага, показывающих состояние обмена: флаг ошибки кадрирования FE n и флаг переполнения DOR n. Флаг FE n устанавливается в «1», если значение первого стоп_бита принятого кадра не соответствует требуемому, т. е. равно «0». Флаги DOR n в USART индицируют потерю данных из_за переполнения буфера приемника. В USART флаг устанавливается в «1» в случае приема старт_бита нового кадра при заполненных буфере и сдвиговом регистре приемника. Установленный флаг DOR n означает, что между прошлым байтом, считанным из регистра UDR, и байтом, считанным в данный момент, произошла потеря одного или нескольких кадров. В модулях USART все флаги ошибок буферизуются вместе со словом данных, т. е. соответствующие разряды регистра UCSR n A относятся к кадру, слово данных которого будет прочитано при следующем обращении к регистру данных UDR n. Поэтому состояние этих флагов должно быть считано перед обращением к регистру данных. Кроме того, для совместимости с будущими устройствами рекомендуется при записи в регистр UCSR n A сбрасывать соответствующие этим флагам разряды записываемого значения в «0». Для индикации состояния приемника в модулях USART используется флаг прерывания «Прием завершен» RXC n регистра UCSR n A. Этот флаг устанавливается в «1» при наличии в буфере приемника непрочитанных данных. В модулях USART — при опустошении буфера (после считывания всех находящихся в нем данных). Выключение приемника осуществляется сбросом разряда RXEN n регистра UCSR n B. В отличие от передатчика приемник выключается сразу же после сброса разряда, т. е. кадр, принимаемый в этот момент, теряется. В модулях USART, кроме того, при выключении приемника очищается его буфер, т. е. теряются также все непрочитанные данные. При выключенном приемнике вывод RXD n может использоваться как контакт вода/вывода общего назначения. Собственно прием всех разрядов кадра осуществляется по_разному, в зависимости от режима работы модуля. При работе модуля USART в синхронном режиме состояние вывода RXD n считывается по одному из фронтов сигнала XCK n. Если разряд UCPOL n регистра UCSR n C сброшен в «0», считывание состояния вывода происходит по спадающему фронту сигнала XCK n, если же установлен в «1» — по нарастающему фронту сигнала. Другими словами, считывание данных с вывода RXD n и их выдача на вывод TXD n происходят по противоположным фронтам (Рис.8.6). Для обеспечения приема в асинхронном режиме работы используются схемы восстановления тактового сигнала и данных. Схема восстановления тактового сигнала предназначена для синхронизации внутреннего тактового сигнала, формируемого контроллером скорости передачи, и кадров, поступающих на вывод RXD n микроконтроллера. Схема восстановления данных осуществляет считывание и фильтрацию каждого разряда принимаемого кадра. Схема восстановления тактового сигнала осуществляет опрос входа приемника с целью определения старт_бита кадра. Частота опроса зависит от состояния разряда U2X n регистра UCSR n A. В обычном режиме (при U2X n = «0») частота опроса в 16 раз превышает скорость передачи данных, а в ускоренном режиме (при U2X = «1») — в 8 раз. Обнаружение изменения сигнала на выводе RXD n с лог. 1 (режим ожидания) на лог. 0 интерпретируется как возможное появление переднего фронта старт_бита. После этого в нормальном режиме проверяется значение 8_й, 9_й и 10_й выборок входного сигнала, а в ускоренном режиме — 4_й, 5_й и 6_й выборок (Рис.8.7 а). Если значение хотя бы двух выборок из указанных равно лог. 1, старт_бит считается ложным (помеха), а приемник переходит к ожиданию следующего изменения входного сигнала с лог. 1 на лог. 0. В противном случае считается, что обнаружен старт_бит новой последовательности, с которым синхронизируется внутренний тактовый сигнал приемника. После этого начинает работать схема восстановления данных. $<_IL_188_189>$

Рис 8.7. Распознавание разрядов кадра: а — старт_бит; б — остальные разряды Решение о значении принятого разряда принимается также по результатам 8_й, 9_й и 10_й (4_й, 5_й и 6_й) выборок входного сигнала (Рис.8.7 б). Состоянием разряда считается логическое значение,которое было получено по меньшей мере в двух из трех выборок. Процесс распознавания повторяется для всех разрядов принимаемого кадра, включая первый стоп_бит. Из сказанного следует, что старт_бит нового кадра может передаваться сразу же после последней выборки, используемой для определения значения разряда. В обычном режиме работы фор мирование старт_бита может начаться в момент A, а в ускоренном режиме — в момент B (Рис.8.8). Момент C, обозначенный на рисунке, определяет максимальную длительность стоп_бита.

Рис.8.8. Распознавание стоп_бита и последующего старт_бита

|