Лабораторна робота № 5.

Дослідження мультиплексорів. Мета: Вивчити алгоритми роботи мультиплексора.

Програмне забезпечення: програмне забезпечення комп'ютерного моделювання електронних схем (програма Electronic Workbench).

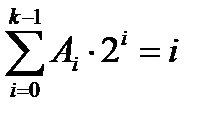

Основні теоретичні відомості Мультиплексор - це комбінаційна багатовхідних схема з одним виходом. Входи мультиплексора поділяються на інформаційні Д 0, Д 1, …, Д n-1 і керуючі (адресні) А 0, А 1, …, А k-1. Зазвичай 2k = n, де k і n – число адресних і інформаційних входів відповідно. Двійковий код, що надходить на адресні входи, визначає (вибирає) один з інформаційних входів, значення змінної з якого передається на вихід y, тобто мультиплексор реалізує функцію:

Варіант схемної реалізації мультиплексора "4-1" ("чотири в один", тобто комутуючого дані від одного з чотирьох входів на єдиний вихід) і його умовне графічне зображення представлені на мал. 1.

Тут мультиплексор побудований як сукупність двохвходових кон'юкторов даних (їх число дорівнює числу інформаційних входів), керованих вихідними сигналами дешифратора, дешіфруючій двійковий адресний код. Виходи кон'юнкторов об'єднані схемою АБО.

Мал. 5.1. Схема мультиплексора з дешифратором (а) і його умовне графічне зображення (б)

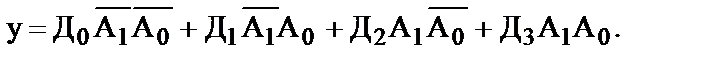

В інтегральному виконанні застосовується більш проста схема, в якій кон'юктори дешифратора одночасно виконують і функцію кон'юнкторов даних. Робота мультиплексора при цьому описується співвідношенням

З (5.2) випливає, що при будь-якому значенні адресного коду всі складові, крім одного дорівнюють нулю. Ненульове доданок одно Дi, де i - значення поточного адресного коду.

Відповідно до цього співвідношенням будуються реальні схеми мультиплексорів, одна з яких для мультиплексора "чотири в один" наведена на мал. 5.2. Як правило, схема доповнюється входом дозволу роботи - Е (показаний пунктирною лінією). При відсутності дозволу роботи (Е = 0) вихід у стає нульовим і не залежить від комбінації сигналів на інформаційних та адресних входах мультиплексора.

Мультиплексори 4-1, 8-1, 16-1 випускаються в складі багатьох серій цифрових інтегральних схем і мають літерний код КП. Наприклад, К555КП1 - мультиплексор 2-1 (в даному корпусі розміщуються чотири мультиплексора), К555КП12 - мультиплексор 4-1 (в одному корпусі розміщуються два мультиплексора) і т.д.

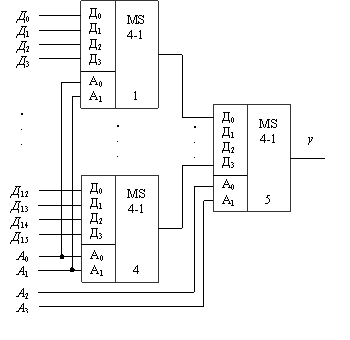

У тих випадках, коли функціональні можливості ІС мультиплексорів не задовольняють розробників по числу інформаційних входів, вдаються до їх каскадування з метою нарощування числа входів до необхідного значення. Найбільш універсальний спосіб нарощування розмірності мультиплексора полягає в побудові пірамідальної структури, що складається з декількох мультиплексорів. При цьому перший ярус схеми є стовпець, що містить стільки мультиплексорів, скільки необхідно для отримання потрібного числа інформаційних входів. Всі мультиплексори цього стовпця комутуються одним і тим же адресним кодом, складеним з відповідного числа молодших розрядів загального адресного коду. Старші розряди адресного коду використовуються у другому ярусі, мультиплексор якого забезпечує почергову роботу мультиплексорів першого ярусу на загальний вихід.

Пірамідальна схема, що виконує функцію мультиплексора "16-1" і побудована на мультиплексорах "4-1", показана на мал. 5.3.

Мал.5.3. Каскадне з'єднання мультиплексорів

|

, если

, если  (5.1)

(5.1)

(5.2)

(5.2)