Лабораторна робота № 2.

Дослідження послідовного та паралельного регістрів. Мета: Побудова схем та вивчення принципу роботи послідовного і паралельного регістрів на D-тригерах.

Програмне забезпечення: програмне забезпечення комп'ютерного моделювання електронних схем (програма Electronic Workbench).

Основні теоретичні відомості Регістром називається послідовнісний цифровий пристрій, що використовується для запису і зберігання n-розрядного двійкового слова. Крім зберігання деякі види регістрів можуть перетворювати інформацію, наприклад, з паралельної в часі форми подання (паралельний код) в послідовну (послідовний код) і навпаки; з прямого коду в зворотний і навпаки; зрушувати інформацію на один або декілька розрядів в сторону молодшого або старшого розрядів.

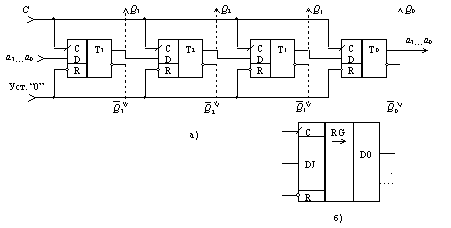

Регістри будуються на базі тригерів, число тригерів у схемі регістра відповідає числу розрядів двійкового слова, що підлягає зберіганню. Розряди регістра крім тригерів можуть містити й деякі ЛЕ, за допомогою яких забезпечується можливість виконання перерахованих вище перетворень інформації. 2.1 Паралельний регістр Паралельним називають регістр, в який n-розрядне двійкове слово записується одночасно по всіх n розрядів. Аналогічним чином здійснюється зчитування зберігається в регістрі слова - одночасно по всьому його розрядами. При зчитуванні інформація, що зберігається в регістрі, зберігається, тобто видається її копія. Паралельний регістр часто іменують регістром пам'яті. Основу регістрів пам'яті складають одноступінчасті синхронні D-або RS-тригери. У цій якості можуть застосовуватися і JK-тригери, але їх можливості більше, ніж потрібно для регістрів пам'яті. Приклад схемної реалізації чотирирозрядний регістра пам'яті наведено на мал. 2.1.

Мал. 2.1. Регістр пам'яті: а) схема, б) умовне зображення

Як елементи регістра тут використані синхронні D-тригери. Зі схеми випливає, що окремі розряди регістра пам'яті не обмінюються даними між собою. Спільними для розрядів регістра є ланцюга управління: синхронізації або дозволу запису (С) і скидання або початкової установки "0". З принципу роботи синхронного D-тригера випливає, що розряди числа А=а 3 а 2 а 1 а 0 запишуться у відповідні тригери Тільки після подачі сигналу (імпульсу) на вхід синхронізації С, тоб при С = 1. Після Зміни сигналу на вході С на "0" тригери переходять в режим зберігання. У цю годину на входь D тригерів можна подати таке слово, наприклад, В=b 3 b 2 b 1 b 0, яке при появі сигналу С = 1 запишеться в регістр. Зчитування слова здійснюється з прямих () виходів тригерів (можливо зчитування і з інверсних виходів - 2.2 Послідовний регістр Послідовним називають регістр, в якому здійснюється послідовний (розряд за розрядом) прийом і видача інформації. Такий регістр часто іменують регістром зсуву або зрушуючим регістром.

Регістр зсуву являє собою ряд послідовно з'єднаних тригерів, число яких визначається розрядністю записуваного в нього слова. У напрямку зсуву записаної в регістр інформації розрізняють регістри прямого зсуву, тобто вправо (в бік молодшого розряду); зворотного зсуву, тобто вліво (в сторону старшого розряду); реверсивні регістри, що допускають зсув в обох напрямках.

На мал. 2.2 наведено приклад схемної реалізації чотирирозрядний регістра зсуву вправо, побудований на синхронізуються фронтом D-тригерах.

Мал. 2.2. Регістр зсуву вправо: а) схема, б) умовне зображення

При запису в регістр двійкового слова А = а3а2а1а0 перший розряд вводиться слова (а0) подається на вхід крайнього лівого тригера (Т3), Що є одночасно входом регістру в цілому, і записується в нього при вступі першого сигналу (імпульсу) синхронізації С. З приходом наступного сигналу синхронізації значення а0 з виходу розряду Q3 вводиться в розряд Q2, а в розряд Q3 надходить а1.

З приходом кожного чергового синхроімпульса виробляється зрушення надходить на один розряд вправо. Після четвертого синхроімпульса регістр виявляється заповненим розрядами слова А і перший розряд слова (а0) з'явиться на виході Q0. Якщо подати на регістр ще одну послідовність з чотирьох синхроімпульсів, встановивши при цьому на його вході рівень "0", то з регістра (з виходу Q0, що є виходом регістра в цілому) буде послідовно виводитися розряди слова А і регістр будуть звільнено від зберігання слова А (очищений).

Таким чином, в процесі зсуву інформації кожен тригер Тi регістра: а) передає збережену інформацію на тригер Тi-1, б) змінює свій стан за рахунок прийому інформації від тригера Тi +1. Передача інформації з тригера Тi і зміна його стану не можуть відбуватися одночасно. Тому основна складність реалізації операції зсуву полягає в поділі в часі виконання зазначених етапів у кожному розряді тригері регістра. Ця складність виключається за рахунок використання синхронних тригерів з динамічним управлінням записом (як показано на мал. 2.2) або двоступеневих тригерів, внутрішня організація яких передбачає поділ у часі етапів прийому вхідної інформації та зміни вихідний.

На мал. 2.3 наведена схема регістра зсуву вліво, побудована на двоступеневих D-тригерах. Комбінуючи схеми зсуву вправо і вліво і використовуючи керуючі сигнали, можна побудувати реверсивний регістр.

Мал. 2.3. Регистр сдвига влево Регістри зсуву (мал. 2.3) дозволяють забезпечити перетворення послідовного коду в паралельний - достатньо в схемі передбачити виходи від всіх розрядів (на мал. 2.2 показані пунктирними лініями).

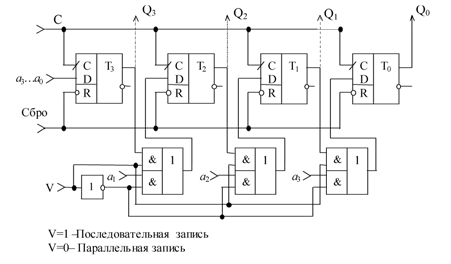

Регістр зсуву легко перетворюється в кільцевої регістр при з'єднанні виходу останнього розряду з входом першого (мал.2.4). Для забезпечення інших видів запису і зчитування застосовуються комбіновані регістри, приклад реалізації одного з яких наведено на мал. 2.5.

Тут двоступеневі логічні елементи І-АБО при V = 1 забезпечують після подачі тактового імпульсу на вхід С передачу сигналу з i-го в i-перше тригер, а при V = 0 забезпечується запис в регістр сигналів, що представляють собою паралельний код. Зчитування записаного довільним способом слова можливе як у вигляді паралельного коду (Q0, Q1, Q2, Q3), так і у вигляді послідовного коду при подачі чотирьох тактових імпульсів.

Мал. 2.5. Комбінований регістр

|

). Для установки тригерів в нульовий стан застосовується спеціальна шина "Уст. "0", пов'язана з асинхронними R-входами кожного тригера.

). Для установки тригерів в нульовий стан застосовується спеціальна шина "Уст. "0", пов'язана з асинхронними R-входами кожного тригера.