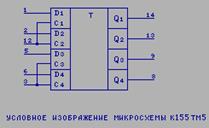

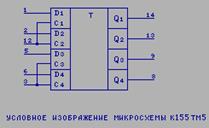

В таких триггерах сигнал (1 или 0) с информационного входа D передается на выход Q в течение всего времени, пока ко входу синхронизации приложен тактовый импульс. Триггер запоминает сигнал, существовавший на информационном входе, перед снятием тактового импульса. На рис.6 приведено условное изображение микросхемы К155ТМ5, содержащей 4 D-триггера со статическим управлением и диаграмма работы одного D-триггера (рис.7).

|

| Рис. 6. Условное изображение микросхемы К155ТМ5

|

|

| Рис. 7. Диаграмма работы одного D-триггера

|

Микросхема имеет два тактовых входа С1 и С2. Триггеры работают самостоятельно, однако тактирование осуществляется попарно. Состояние триггера меняется в соответствии с состоянием информационного входа, когда вход синхронизации находится в состоянии логической 1. При переходе тактового импульса в состояние логического нуля триггер запоминает записанную в нем информацию, и состояние его остается неизменным независимо от состояния информационного входа.