Если мощность SСР(w) шума, генерируемого ЧФД, пересчитать на его вход, разделив на коэффициент передачи ЧФД, т.е.

QCP(w) = SСР(w) |Hзам(jw)/Kd(jw)|2,

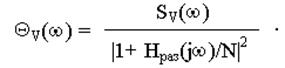

то выводы о влиянии шумов и помех, порождаемых ЧФД, на спектр выходного колебания синтезатора будут аналогичны сделанным выше для QR(w). Противоположным образом, как ФВЧ, действует петля ФАПЧ на собственные шумы ГУН («внутренние» шумы): она подавляет низкочастотные флуктуации фазы ГУН и пропускает высокочастотную их составляющую (границей раздела областей НЧ и ВЧ здесь опять служит частота W1). Чтобы убедиться в этом, выпишем выражение для QV(w) – части мощности выходного фазового шума, обусловленной наличием SV(w):

Поскольку Hраз(p) является функцией, обладающей свойствами ФНЧ, см. рис. 7.4.4, то в области низких частот |Hраз(jw)/N| >> 1 и, соответственно, QV(w)» 0. Напротив, при w>>W1 будет выполняться неравенство |Hраз(jw)/N|» 0, откуда следует, что подавления высокочастотных флюктуаций фазы ГУН не будет: QV(w) = SV(w). Иллюстрацией к вопросу о фильтрации фазовых шумов петлей ФАПЧ может послужить рис. 7.4.5, где на спектре выходного колебания синтезатора на основе ИМС ADF4113, имеющего центральную частоту 900 МГц, можно четко различить две частотные области: низкочастотная - «внешних» шумов, главным источником которых является колебание опорного генератора, и высокочастотная - «внутренних» шумов, связанная с флюктуациями фазы ГУН. Границей раздела (cм. W1 на рис. 7.4.4) этих областей является частота среза петли, в данном случае равная 20 кГц.

Рис. 7.4.5

Итак, в случае применения простой однопетлевой (однокольцевой) системы ФАПЧ возникает противоречие: для того, чтобы уменьшить влияние фазовых шумов ГУН, необходимо уменьшать инерционность петлевого фильтра, а для снижения проникновения в выходное колебание «внешних» фазовых шумов, нужно действовать противоположным образом, т.е. «утяжелять» фильтр. Иногда эту проблему решают с помощью введения в систему ФАПЧ дополнительных петель авторегулирования. Рассмотрим для примера двухкольцевую систему ФАПЧ (рис. 7.4.6).

Рис.7.4.6

Внутреннее кольцо этой системы состоит из фазового дискриминатора ФД2, петлевого фильтра ФНЧ2, генератора ГУН2 и делителя частоты с переменным коэффициентом деления N ДПКД2. Фильтр ФНЧ2 делается малоинерционным для того, чтобы успешно подавлять шумы выходного генератора всей системы – ГУН2. Внешнее кольцо ФАПЧ включает в себя элементы ДПКД3 с коэффициентом деления частоты L, ФД1, опорный кварцевый генератор ОГ, ФНЧ1, ГУН1 и ДПКД1 с коэффициентом деления частоты М. Петлевой фильтр внешнего кольца ФНЧ1 является весьма инерционным, за счет чего фазовый шум генератора ГУН1 значительно меньше, чем шум опорного генератора ОГ. Таким образом, для внутреннего кольца ФАПЧ ПГ1 выступает в качестве эталонного малошумящего генератора, следовательно, общий уровень шума в выходном колебании двухкольцевой системы ФАПЧ должен быть меньше, чем у типовой однокольцевой. Из рис. 7.4.6 видно, что в процессе работы двухкольцевой системы ФАПЧ должны одновременно выполняться два условия:

Можно сделать вывод, что для правильного функционирования рассматриваемого синтезатора при смене частоты коэффициент L должен изменяться синхронно с коэффициентами M и N:

Иногда для оптимизации характеристик системы ФАПЧ ее выполняют многокольцевой – может использоваться три кольца авторегулирования и больше; возможен вариант совмещения в одной системе колец фазовой и частотной автоподстройки частоты. Вернемся к простому синтезатору с ФАПЧ по схеме рис. 7.4.1. Для повышения рабочей частоты синтезатора перед ДПКД (который может работать на частотах только до сотен МГц) устанавливают предварительный делитель частоты с коэффициентом деления К, при этом и шаг перестройки частоты увеличивается в К раз:

F вых = (К · F 0 / M)N.

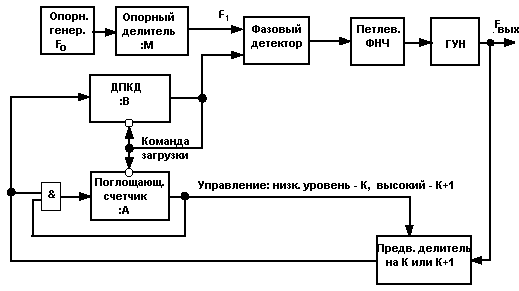

В случае необходимости сохранения на высоких рабочих частотах такого же шага перестройки, как в схеме без предварительного делителя (F 0 / M) применяют схему с перестраиваемым поглощающим счетчиком и двухмодульным предварительным делителем (рис.7.4.7).

Рис. 7.4.7.

Предварительный делитель в этой схеме имеет переключаемый коэффициент деления: К или К+ 1 (например, 10/11 или 3/4, такие ИМС выпускаются промышленностью). ДПКД и поглощающий счетчик работают таким образом, что по команде загрузки они загружаются числом В и А соответственно (причем обязательно В>А), после чего каждый входной импульс уменьшает их состояние на 1. Пока в счетчиках остается число, большее 0, на их выходах присутствует высокий логический уровень, а при достижения 0 этот уровень меняется на низкий. Схема с поглощающим счетчиком работает следующим образом. Пусть в какой-то момент времени счетчик В обнулился, при этом оба счетчика, согласно схеме, перезагружаются величинами А и В соответственно, и начинается новый цикл счета на уменьшение их значений. Пока поглощающий счетчик не обнулился, на его выходе 1 и предварительный делитель работает с коэффициентом К+ 1, поэтому он обнулится через (К+1) А периодов частоты ГУН. Как только его значение достигнет 0, на его выходе установится низкий логический уровень, он перестанет считать, а коэффициент предварительного делителя станет равным К. До обнуления счетчика В останется еще (В-А) циклов счета (счетных импульсов). Поскольку счетные импульсы теперь поступают с частотой ГУН, деленной на К, то до обнуления счетчика В пройдет еще (В-А)К периодов частоты ГУН. После обнуления ДПКД описанный цикл повторится. Итак, подсчитаем эквивалентный коэффициент деления схемы: он равен полному числу периодов частоты ГУН до ее повторной перезагрузки

N = (A(K+1))+((B-A)K) = A+BK.

Частота ГУН при этом описывается той же формулой, что и для простейшей петли ФАПЧ:

F вых = (F 0 / M)N = (F 0 / M)(A+BK)

Важно здесь то, что теперь изменением коэффициента деления поглощающего счетчика А можно добиться перестройки синтезатора на высокой частоте с малым шагом, равным (F 0 / M). Пределы изменения эквивалентного коэффициента деления N = (К2-К)... (Amax+BmaxK). Описанный принцип реализован в отечественных ИМС К1015ХК2А (им требуется внешний предварительный делитель с изменяемым модулем счета) и в ИМС семейства ADF4110-ADF4112 (у них этот делитель выполнен на кристалле ИМС). Рассмотренные выше типы синтезаторов (рис. 7.4.1., рис. 7.4.7) относятся к классу синтезаторов с целочисленным коэффициентом деления частоты N в цепи обратной связи, или «Integer-N» синтезаторам. Существуют синтезаторы с дробно-переменным делителем частоты (ДДПКД), называемые «Fractional-N» синтезаторами, у которых N может иметь изменяемую дробную часть. Их преимуществом является возможность получения заданной рабочей частоты при значительно меньшем коэффициенте деления в цепи обратной связи петли ФАПЧ. При этом обеспечивается и малый шаг сетки частот синтезатора. Напомним, что из полученной выше формулы QR(w) = N2SR(w), описывающей влияние фазовых шумов опорного генератора на СПМ фазовых шумов выходного колебания синтезатора, следует, что для улучшения спектральной чистоты выходного колебания желательно работать с небольшими значениями N, что невозможно обеспечить для высоких частот синтезатора при малом шаге по частоте. Длительность переходных процессов в синтезаторе также определяется шагом по частоте, который, как было отмечено выше, для любого «Integer-N» синтезатора равен частоте сравнения (F 0 / M). Проиллюстрируем сказанное примером. Предположим, требуется получить сетку частот в окрестности 50 МГц с шагом 10 Гц. Частота опорного кварцевого генератора составляет F 0 = 1 МГц. В случае применения простой однокольцевой схемы ФАПЧ (рис.7.4.1) коэффициент деления ДПКД составит N = 5000000, коэффициент деления опорного делителя М = 100000. Величина СКО фазового шума опорного генератора, пересчитанная на выход синтезатора, т.е. проникающая в спектр колебания ГУН, будет в N/M = 50 раз больше, чем СКО фазового шума самого опорного генератора. Длительность же переходного процесса установления новой частоты может достигать 10…100 периодов частоты сравнения дискриминатора, что в данном случае составит 1…10 секунд! Рассмотрим тот же пример при использовании синтезатора частоты с дробно-переменным коэффициентом N («Fractional-N» синтезатора). Существует несколько различных схем таких синтезаторов, но для любой из них можно записать формулу, определяющую значение частоты выходного колебания в следующем виде:

F вых = F сравн(N+q/MF),

где F сравн – частота сравнения ЧФД, причем, как и для рассмотренных выше схем синтезаторов справедливо соотношение F сравн = F 0/ М; N – целая часть коэффициента деления ДДПКД; q – число, записанное в «дробный» регистр, MF – значение «модуля-интерполятора»; 0 £ q £ MF. Итак, выбираем частоту сравнения F сравн = 100 кГц; длительность переходного процесса определяется этой частотой и достигает 0,1…1 мс, но шаг перестройки частоты зависит не от частоты сравнения, а от значения модуля-интерполятора. Установив значение «целочисленного» регистра ДДПКД N = 500 и значение модуля-интерполятора MF = 10000, получим: для q = 0 F вых = 50 МГц, для q = 1 F вых = 50,00001 МГц и т.д., следовательно, шаг перестройки по частоте составит требуемую величину 10 Гц. Рассмотрим упрощенный вариант структурной схемы синтезатора с ДДПКД [20], рис. 7.4.8. Узлы опорного генератора ОГ, опорного делителя частоты ОД, частотно-фазового дискриминатора ЧФД, петлевого ФНЧ и ГУН являются типовыми для любой схемы ФАПЧ и аналогичны рассмотренным выше. Делитель с переменным коэффициентом деления в данной схеме двухмодульный: при подаче на его управляющий вход s логического нуля коэффициент деления равен N, а при s равном логической единице он принимает значение N +1. Управляющий сигнал вырабатывается счетчиком импульсов СИ, имеющим вход для счетных импульсов и импульса сброса содержимого в логический 0. В счетчик СИ пользователем записывается число q, которое служит для сравнения с числом подсчитанных импульсов, поступающих на вход «счет». Выход счетчика СИ равен логической 1 до тех пор, пока содержимое его меньше или равно q, а после того, как счетчиком будет получен q +1 счетный импульс, его выход устанавливается в логический 0. Импульс сброса содержимого счетчика СИ в 0 вырабатывается другим счетчиком – накопителем кода фазы НКФ, который подсчитывает импульсы, следующие с частотой сравнения с выхода опорного делителя частоты. Модуль счета НКФ также определяется пользователем и обозначен здесь как MF; после формирования сбрасывающего импульса, обнуляющего содержимое СИ, содержимое НКФ также обнуляется.

Рис. 7.4.8.

Начнем рассмотрение работы схемы рис. 7.4.8 с того момента, когда содержимое НКФ и СИ стало равным нулю. Первые q импульсов ГУН с этого момента будут делиться в ДПКД на N +1, а последующие, начиная с q +1 и до прихода с НКФ импульса «сброс», будут делиться по частоте на N. В синхронном режиме периоды импульсных последовательностей на обоих входах ЧФД равны, что можно выразить в виде очевидного равенства, левая часть которого эквивалентна количеству периодов частоты сравнения, поступающих на опорный вход ЧФД, а правая – количеству периодов импульсной последовательности, поступающей на ЧФД с ДПКД за интервал времени между двумя последовательными переполнениями НКФ:

Выражая выходную частоту синтезатора F вых = f ГУН из данного равенства, получим:

Этой формулой мы уже пользовались выше для описания свойств «Fractional-N» - синтезатора. Таким образом, синтезаторам частоты с дробно-переменным коэффициентом деления присуще полезное свойство – возможность обеспечение малого шага сетки частот при высоких значениях самой рабочей частоты. Тем не менее, из самого принципа его работы очевиден и его недостаток: постоянное переключение коэффициента деления частоты в ДПКД приводит к паразитной частотной модуляции и, следовательно, появлению нежелательных частотных составляющих в спектре выходного колебания. На рис. 7.4.9 можно увидеть график упрощенной зависимости частоты выходного колебания синтезатора с ДДПКД вида N /(N +1) от времени. Для устранения указанного нежелательного эффекта в выпускаемых промышленностью «Fractional-N»-синтезаторах применяют следующие меры: - усложняют ДДПКД, предусматривая в нем переключение нескольких коэффициентов деления частоты, например, N, N +1, N -1; - используют сигма-дельта корректор, который псевдослучайным образом нарушает регулярность переключений коэффициента деления, что помогает «размывать» наиболее интенсивные спектральные составляющие, но увеличивает мощность фазового шума; - выбирают определенный алгоритм переключения коэффициента деления частоты; - включают управляемую линию задержки на выходе ГУН [20].

Рис.7.4.9.

В качестве примера интегрального исполнения «Fractional-N» -синтезатора рекомендуем изучить материалы по ИМС семейства AD4250..AD4252 фирмы Analog Devices. В цифровых приемопередатчиках широко используют сдвоенные синтезаторы частоты - микросхемы, способные формировать одновременно две частоты от одного опорного сигнала. Сдвоенные синтезаторы частоты можно разделить на два типа: ВЧ/ВЧ синтезаторы, вырабатывающие одновременно две высокие частоты, номиналы которых различаются незначительно, и ВЧ/ПЧ синтезаторы, у которых номиналы частот различаются более чем на порядок. В последнем случае ВЧ колебание может вырабатываться с использованием схемы «Fractional-N», а колебание промежуточной частоты - схемой «Integer-N» сдвоенного синтезатора. При этом обе системы ФАПЧ, размещенные на кристалле сдвоенного синтезатора, тактируются от одного опорного генератора, за счет чего их колебания получаются когерентными; благодаря этому обеспечивается возможность когерентной обработки сигналов цифровой радиосвязи [21]. Строго говоря, рассмотренные выше системы ФАПЧ нельзя назвать в полном смысле цифровыми: точнее было бы говорить об импульсных системах ФАПЧ с цифровыми узлами. В настоящее время разрабатываются полностью цифровые системы ФАПЧ, в которых цифровыми методами реализуются все узлы системы, в том числе ЧФД, петлевой фильтр, управляемый генератор; частота последнего в данном случае зависит не от управляющего напряжения, а от кода. Для дальнейшего изучения интегральных систем ФАПЧ рекомендуем ознакомиться с главой 12 книги [22] – «Проблемы разработки систем ФАПЧ с использованием глубокой субмикронной технологии». Может быть также полезным для читателей, заинтересовавшихся работой синтезаторов с ФАПЧ, обращение к Интернет-ресурсу www.analog.com/pll/, где представлена интерактивная программа ADIsimPLL, помогающая оценить работу синтезаторов на основе ИМС семейств ADFхххх (ADF4000…4117, ADF4252 и т.д.). Существуют аналогичные «виртуальные» возможности и у других производителей интегральных систем ФАПЧ.

|