Условия возникновения выбросов

СИТУАЦИИ РИСКА В ЛОГИЧЕСКИХ СХЕМАХ Введение Во многих случаях неправильная работа реальных логических схем может объясняться наличием с них ситуаций риска, поэтому для разработчика логических схем необходимо иметь ясное представление о причинах появления таких ситуаций и знать об их влиянии на работу схем. Существует три типа риска в логических схемах: а) статический риск; б) динамический риск; в) существенный риск. Статический и динамический риск может возникнуть в комбинационных, а также в асинхронных схемах, реализованных на логических элементах. Существенный риск может возникать только в асинхронных схемах. В этой главе описываются случаи появления ситуаций риска в логических схемах, а также излагаются методы их обнаружения. Кроме этого, приводятся методы проектирования, позволяющие избавляться от ситуаций риска.

Явления временной задержки в логических элементах

Если в комбинационной схеме в качестве инвертора используется двухвходовый логический элемент И-НЕ, как показано на рис. 11.1, то между требуемым изменением на выходе и вызывающим его изменением на входе существует конечная временная задержка t g. Это показано на временных диаграммах, из которых видно, что в результате изменения А от 0 до 1 изменение А от 1 до 0 происходит на t g секунд позднее. Аналогично этому, при изменении А от 1 до 0 соответствующее изменение А от 0 до 1 осуществится также на t g позднее. Условия возникновения выбросов Если, как показано па рис. 11.2, на входы элемента И подаются одновременно сигнал А и его отрицание

Схему, в которой возможна генерация сигнала В другом случае, если сигналы А и

11.4. Возникновение ситуаций статического риска в комбинационных схемах При изменении входных сигналов комбинационной схемы на ее выходе могут возникнуть выбросы. Они появляются из-за того, что на различных путях прохождения сигналов через схему от входа к ее выходу могут возникать различные временные задержки. Например, булева функция вида

может быть реализована с помощью изображенной на рис. 11.5 схемы из элементов И-НЕ. Сигналы через эту схему проходят по двум путям: первый - через элементы g 1, g 2 и g 3 и второй - через g 4 и g 3. Если считать, что все элементы имеют одинаковую временную задержку, равную tg с, то очевидно, что задержка, возникающая на первом пути, больше задержки на втором.

Поскольку было принято, что В = 1 и С = 1, уравнение схемы упрощается до выражения

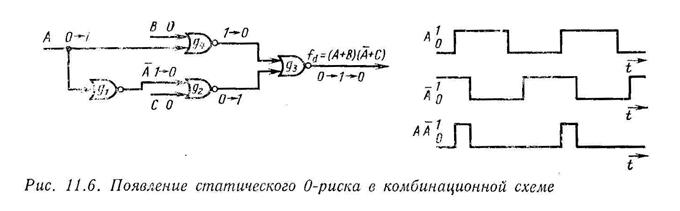

На рис. 11.6 показано, как можно реализовать это равенство с помощью элементов ИЛИ-НЕ. При условии, что В = 0 и С = О уравнение этой схемы упрощается до вида  . Если можно выполнить такое упрощение, появляется вероятность статического 0-риска для схемы, реализующей уравнение . Если можно выполнить такое упрощение, появляется вероятность статического 0-риска для схемы, реализующей уравнение  . Сразу после изменения А из 0 в 1 сигналы А и . Сразу после изменения А из 0 в 1 сигналы А и  одновременно равны 1 и, следовательно, одновременно равны 1 и, следовательно,  . Это значение остается до тех пор, пока сигнал А не станет равным 0 и вновь не восстановится значение . Это значение остается до тех пор, пока сигнал А не станет равным 0 и вновь не восстановится значение  равное 0. равное 0.

Изменения сигналов в схеме также показаны на рис. 11.6 при условии, что В = С = 0, а сигнал А изменяется из 0 в 1. Если все элементы схемы имеют одинаковую временную задержку, равную t g, то путь g 4, g 3 имеет минимальное время задержки, и изменение А от 0 до 1 достигнет выхода по этому пути быстрее, чем по пути g 1, g 2, g 3, что приведет к изменению на выходе от 0 до 1. Когда то же самое изменение сигнала А попадет на выход схемы по другому пути, то выходной сигнал станет равен 0.

|

. Однако, как можно видеть на временных диаграммах, в течение интервалов времени, отмеченных штриховкой, А и

. Однако, как можно видеть на временных диаграммах, в течение интервалов времени, отмеченных штриховкой, А и  . Выходная функция этого элемента, равная

. Выходная функция этого элемента, равная  , состоит из серии положительных выбросов, возникающих при изменении А от 0 до 1 и имеющих длительность в t g с. Это явление, безусловно, объясняется временной задержкой логического инвертора, показанного на рис. 11.1.

, состоит из серии положительных выбросов, возникающих при изменении А от 0 до 1 и имеющих длительность в t g с. Это явление, безусловно, объясняется временной задержкой логического инвертора, показанного на рис. 11.1.

, которая в соответствии с алгеброй логики должна быть равна логической «1». Расположение импульсов А и

, которая в соответствии с алгеброй логики должна быть равна логической «1». Расположение импульсов А и

. Поэтому в начале этого интервале времени сигнал

. Поэтому в начале этого интервале времени сигнал  изменяется из 1 в 0, возвращаясь назад, когда

изменяется из 1 в 0, возвращаясь назад, когда